# FACULTAD DE EDUCACIÓN TÉCNICA PARA EL DESARROLLO CARRERA DE INGENIERÍA EN TELECOMUNICACIONES

#### TEMA:

Desarrollo de aplicaciones prácticas de sistemas combinatoriales de compuertas digitales utilizando instrumentación virtual LabVIEW

#### **AUTOR:**

Plaza Calderón, Martin Fernando

Componente práctico del examen complexivo, previo a la obtención del grado de **INGENIERO EN TELECOMUNICACIONES**

**REVISOR:**

M. Sc. Pacheco Bohórquez, Héctor Ignacio

Guayaquil, Ecuador

6 de marzo del 2020

FACULTAD DE EDUCACIÓN TÉCNICA PARA EL DESARROLLO

CARRERA DE INGENIERÍA EN TELECOMUNICACIONES

# **CERTIFICACIÓN**

Certificamos que el presente componente práctico del examen complexivo, fue realizado en su totalidad por Plaza Calderón, Martin Fernando como requerimiento para la obtención del título de INGENIERO EN TELECOMUNICACIONES.

| REVISOR                                  |  |  |  |  |

|------------------------------------------|--|--|--|--|

|                                          |  |  |  |  |

|                                          |  |  |  |  |

| M. Sc. Pacheco Bohórquez, Héctor Ignacio |  |  |  |  |

|                                          |  |  |  |  |

|                                          |  |  |  |  |

| DIRECTOR DE CARRERA                      |  |  |  |  |

|                                          |  |  |  |  |

| M. O. Hanna Oʻzaka — Missaal Assaarda    |  |  |  |  |

| M. Sc. Heras Sánchez, Miguel Armando     |  |  |  |  |

Guayaquil, 6 de marzo del 2020

FACULTAD DE EDUCACIÓN TÉCNICA PARA EL DESARROLLO

CARRERA DE INGENIERÍA EN TELECOMUNICACIONES

### **DECLARACIÓN DE RESPONSABILIDAD**

Yo, Plaza Calderón, Martin Fernando

#### **DECLARÓ QUE:**

El componente práctico del examen complexivo: Desarrollo de aplicaciones prácticas de sistemas combinatoriales de compuertas digitales utilizando instrumentación virtual LabVIEW, ha sido desarrollado respetando derechos intelectuales de terceros conforme las citas que constan en el documento, cuyas fuentes se incorporan en las referencias o bibliografías. Consecuentemente este trabajo es de mi total autoría.

En virtud de esta declaración, me responsabilizo del contenido, veracidad y alcance del Trabajo de Titulación referido.

Guayaquil, 6 de marzo del 2020

**EL AUTOR**

\_\_\_\_\_

PLAZA CALDERÓN, MARTIN FERNANDO

FACULTAD DE EDUCACIÓN TÉCNICA PARA EL DESARROLLO

CARRERA DE INGENIERÍA EN TELECOMUNICACIONES

# **AUTORIZACIÓN**

Yo, Plaza Calderón, Martin Fernando

Autorizó a la Universidad Católica de Santiago de Guayaquil a la publicación en la biblioteca de la institución del componente práctico del examen complexivo: Desarrollo de aplicaciones prácticas de sistemas combinatoriales de compuertas digitales utilizando instrumentación virtual LabVIEW, cuyo contenido, ideas y criterios son de mi exclusiva responsabilidad y total autoría.

Guayaquil, 6 de marzo del 2020

**EL AUTOR**

\_\_\_\_\_

PLAZA CALDERÓN, MARTIN FERNANDO

#### REPORTE DE URKUND

### **DEDICATORIA**

Es mi deseo como sencillo gesto de agradecimiento, dedicarle este trabajo de titulación a mi madre Ligia, por su amor incondicional y por ser el pilar fundamental que me permitió perseverar hasta cumplir mi objetivo.

A mi padre, mi hermana y mis abuelitos, por su permanente cariño y comprensión, quienes siempre me brindaron todo su apoyo y nunca dejaron de creer en mí.

**EL AUTOR**

PLAZA CALDERÓN, MARTIN FERNANDO

#### **AGRADECIMIENTO**

Quiero agradecer a Dios, quién con su bendición llena siempre mi vida.

A mi familia por estar siempre presentes y darme un gran ejemplo de trabajo y honradez.

De manera especial al revisor y Coordinador de Titulación, por haberme guiado, no solo en la elaboración de este trabajo de titulación, sino a lo largo de mi carrera universitaria y haberme brindado el apoyo para desarrollarme profesionalmente y seguir cultivando mis valores.

A la Universidad Católica Santiago de Guayaquil, por haberme brindado tantas oportunidades y enriquecerme en conocimiento.

**EL AUTOR**

PLAZA CALDERÓN, MARTIN FERNANDO

# FACULTAD DE EDUCACIÓN TÉCNICA PARA EL DESARROLLO CARRERA DE INGENIERÍA EN TELECOMUNICACIONES

## TRIBUNAL DE SUSTENTACIÓN

| f                                                           |

|-------------------------------------------------------------|

| M. Sc. ROMERO PAZ, MANUEL DE JESÚS<br>DECANO                |

|                                                             |

|                                                             |

| f                                                           |

| M. Sc. HERAS SÁNCHEZ, MIGUEL ARMANDO<br>DIRECTOR DE CARRERA |

|                                                             |

f.\_\_\_\_\_ M. Sc. PALACIOS MELÉNDEZ, EDWIN FERNANDO OPONENTE

# **ÍNDICE GENERAL**

| Capít  | ulo 1: D                                                                     | escripción del componente práctico                       | 2   |  |  |

|--------|------------------------------------------------------------------------------|----------------------------------------------------------|-----|--|--|

| 1.1.   | Introducción                                                                 |                                                          |     |  |  |

| 1.2.   | Objetivo General                                                             |                                                          |     |  |  |

| 1.3.   | Objetivos Específicos                                                        |                                                          |     |  |  |

| Capít  | ulo 2: F                                                                     | undamentación teórica                                    | 4   |  |  |

| 2.1.   | Introducción del uso de herramientas de simulación                           |                                                          |     |  |  |

| 2.2.   | Kit de l                                                                     | herramientas basado en VHDL                              | 5   |  |  |

| 2.3.   | Desarrollo de herramientas en NI LabVIEW7                                    |                                                          |     |  |  |

|        | 2.3.1.                                                                       | Compuertas lógicas básicas en LabVIEW                    | 7   |  |  |

|        | 2.3.2.                                                                       | Dispositivos combinatorios en LabVIEW                    | 8   |  |  |

|        | 2.3.3.                                                                       | Dispositivos secuenciales                                | 9   |  |  |

| Capít  | ulo 3: Di                                                                    | iseño y análisis de resultados                           | .10 |  |  |

| 3.1.   | Descri                                                                       | pción general del componente práctico                    | .10 |  |  |

| 3.2.   | Descri                                                                       | Descripción general de LabVIEW11                         |     |  |  |

|        | 3.2.1.                                                                       | Panel frontal                                            | .11 |  |  |

|        | 3.2.2.                                                                       | Panel de bloque                                          | .12 |  |  |

|        | 3.2.3.                                                                       | Panel de iconos y conectores.                            | .12 |  |  |

| 3.3.   | Desarrollo de aplicaciones prácticas de circuitos combinatoriales en LabVIEW |                                                          |     |  |  |

|        | 3.3.1.                                                                       | Escenario práctico 1: Aplicación de compuertas lógicas   | .14 |  |  |

|        | 3.3.2.                                                                       | Escenario práctico 2: Aplicación de lógica combinatorial | .27 |  |  |

| Conc   | lusiones                                                                     |                                                          | .36 |  |  |

| Reco   | mendac                                                                       | iones                                                    | .37 |  |  |

| Biblio | grafía                                                                       |                                                          | .38 |  |  |

# **ÍNDICE DE FIGURAS**

| Capítulo 2:                                                                   |

|-------------------------------------------------------------------------------|

| Figura 2. 1: Instrumento virtual del nodo de interfaz HDL                     |

| Figura 2. 2: Estructura de VIs polimórficos                                   |

| Figura 2. 3: Instrumentos de compuertas lógicas en LabVIEW                    |

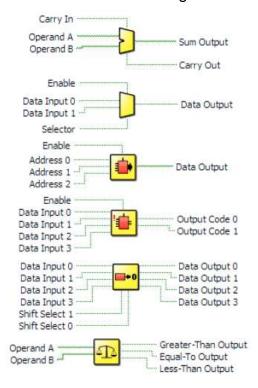

| Figura 2. 4: Instrumentos de dispositivos combinatoriales en LabVIEW8         |

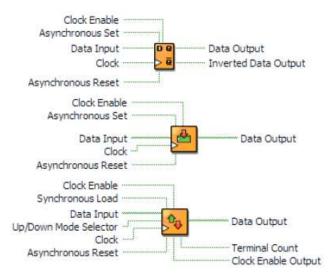

| Figura 2. 5: Instrumentos de dispositivos secuenciales en LabVIEW9            |

|                                                                               |

| Capítulo 3:                                                                   |

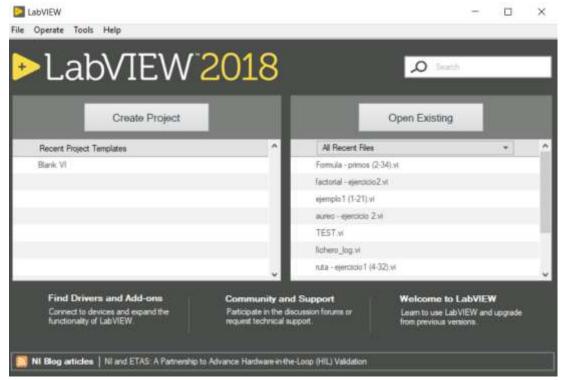

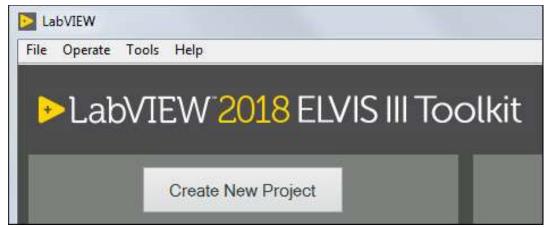

| Figura 3. 1: Ventana principal del software LabVIEW 20181                     |

| Figura 3. 2: Ventana de trabajo del panel frontal en LabVIEW12                |

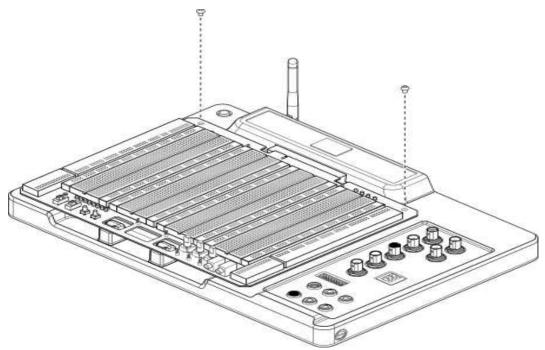

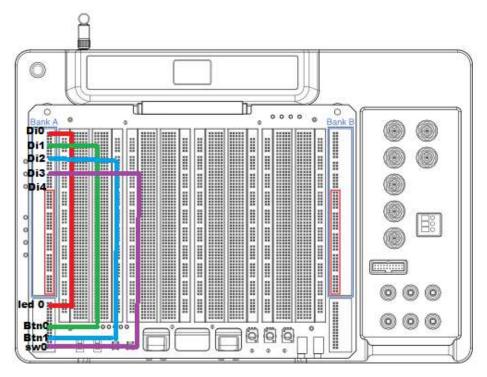

| Figura 3. 3: Conexión de la antena al equipo Elvis III de NI13                |

| Figura 3. 4: Conexión de la antena al equipo Elvis III de NI13                |

| Figura 3. 5: Conexión de la antena al equipo Elvis III de NI14                |

| Figura 3. 6: Ventana de configuración de dispositivos detectados en NI Elvis  |

| III                                                                           |

| Figura 3. 7: Ventana de instalación del software NI Elvis III15               |

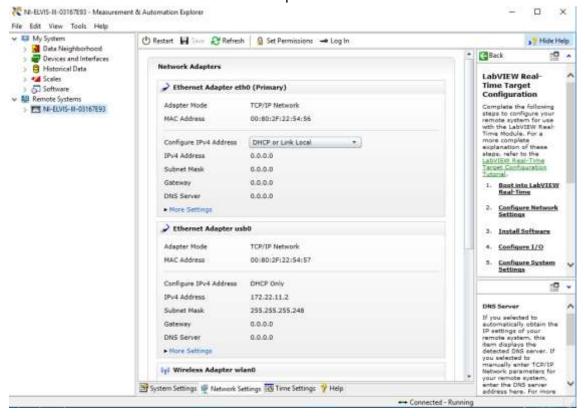

| Figura 3. 8: Ventana de configuración para redes de NI Elvis III16            |

| Figura 3. 9: Ventana de configuración de adaptadores de redes de NI Elvis III |

| 16                                                                            |

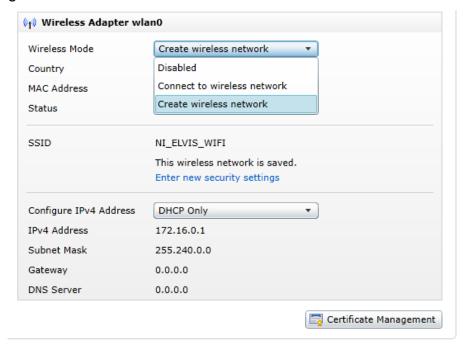

| Figura 3. 10: Ventana de configuración del adaptador WLAN de NI Elvis III     |

| 17                                                                            |

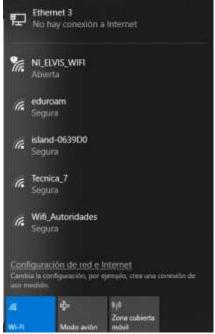

| Figura 3. 11: Selección de la red NI_ELVIS_WIFI17                             |

| Figura 3. 12: Creación de un nuevo proyecto en LabVIEW18                      |

| Figura 3. 13: Elección del tipo de proyecto mediante NI ELVIS III18           |

| Figura 3. 14: Configuración de un nuevo proyecto en LabVIEW para conecta      |

| a WiFi19                                                                      |

| Figure 3, 15: Creación de un nuevo proyecto en LabVIEW                        |

| Figura 3. 16: Ventanas del panel de control y bloque de diagrama para la primera aplicación práctica |

|------------------------------------------------------------------------------------------------------|

| Figura 3. 17: Establecer la lectura de un valor digital mediante el botón Elvis                      |

| Figura 3. 18: Ejecución de un flat secuencial en tres procesos2                                      |

| Figura 3. 19: Circuito de conmutación mediante lógica binaria2                                       |

| Figura 3. 20: Creación de un nuevo proyecto en LabVIEW22                                             |

| Figura 3. 21: Configuración de salidas digitales para la aplicación práctica 1                       |

| Figura 3. 22: Bloque de diagrama con las salidas digitales incorporadas para esta práctica 1         |

| Figura 3. 23: Conexiones de salidas digitales en la Elvis III para práctica 1.24                     |

| Figura 3. 24: Creación de controles de entrada/salida (I/O) para práctica 1.24                       |

| Figura 3. 25: Configuración de entradas digitales para la aplicación práctica 1                      |

| Figura 3. 26: Conexiones de entradas digitales en la Elvis III para práctica 1                       |

| Figura 3. 27: Instrumentos virtuales booleanos para la función S de la práctica 1                    |

| Figura 3. 28: Bloque de diagrama con el diseño de la función lógica digital. 26                      |

| Figura 3. 29: Diseño final en el bloque de diagrama para la práctica 127                             |

| Figura 3. 30: Creación de controles de entrada/salida (I/O) para práctica 2.28                       |

| Figura 3. 31: Configuración de salidas digitales para la aplicación práctica 2                       |

| Figura 3. 32: Bloque de diagrama con las salidas digitales incorporadas para esta práctica 2         |

| Figura 3. 33: Conexiones de salidas digitales en la Elvis III para práctica 2.30                     |

| Figura 3. 34: Creación de un nuevo proyecto en LabVIEW30                                             |

| Figura 3. 35: Configuración de entradas digitales para la aplicación práctica 2                      |

|                                                                                                      |

| Figura 3. 36: Conexiones de entradas digitales en la Elvis III para práctica 231  |

|-----------------------------------------------------------------------------------|

| Figura 3. 37: Instrumentos virtuales booleanos para la función S de la práctica 2 |

| Figura 3. 38: Diseño final en el bloque de diagrama para la práctica 232          |

| Figura 3. 39: Resultado obtenido en la práctica 1 cuando A=0 y B=C=133            |

| Figura 3. 40: Resultado obtenido en la práctica 1 cuando A=0 y B=C=133            |

| Figura 3. 41: Resultado obtenido en la práctica 1 cuando A=B=0 y B34              |

| Figura 3. 42: Resultado obtenido en la práctica 1 cuando A=B=C=134                |

| Figura 3. 43: Resultado obtenido en la práctica 2 cuando A=1 y B=C=035            |

| Figura 3. 44: Resultado obtenido en la práctica 2 cuando A=B=C=135                |

| Figura 3. 45: Resultado obtenido en la práctica 2 cuando A=B=1, C=035             |

#### Resumen

El trabajo del componente práctico del examen complexivo trata del desarrollo de aplicaciones prácticas de sistemas combinatoriales de compuertas digitales utilizando instrumentación virtual LabVIEW de National Instruments, este desarrolló un juego de herramientas de diseño de lógica digital que se integró en el software y que permite a los estudiantes diseñar utilizando dispositivos lógicos combinatorios y secuenciales típicos que iban desde compuertas lógicas AND, OR, NOT, XOR, NAND, NOR, XNOR hasta Flip-Flops, contadores, los dispositivos comparadores, decodificadores, entre otros. La electrónica digital es la columna vertebral de la tecnología actual, juega un papel fundamental en el crecimiento de la humanidad. La memoria digital es parte de la electrónica digital y consiste en bloques de construcción de Flip-Flops diseñados mediante el uso de puertas lógicas NAND y NOR. La validación del almacenamiento de información en forma de bits puede entenderse a partir del análisis del funcionamiento de flipflops. Finalmente, este proyecto permite disponer de una ayuda académica en la enseñanza de los sistemas digitales.

Palabras claves: INSTRUMENTOS, VIRTUALES, LÓGICA, SECUENCIAL, COMBINATORIAL, MEMORIA

## Capítulo 1: Descripción del componente práctico.

#### 1.1. Introducción.

La implementación de los planes de estudio actuales generalmente implica importantes recursos materiales, y más específicamente, laboratorios para llevar a cabo la parte práctica de los cursos. Esto significa un costo importante, tanto desde el punto de vista económico como del espacio físico necesario para instalarlos. Estos recursos no están disponibles para muchas de las Escuelas de Ingeniería. (Amer et al., 2015)

El papel de la experimentación en la educación técnica no puede exagerarse. La experiencia de laboratorio agrega una dimensión que permite a los estudiantes apreciar conceptos teóricos y adquirir valiosas habilidades profesionales. Los rápidos cambios en la tecnología plantean una necesidad continua de actualizar y aumentar el trabajo de laboratorio para mantener el ritmo de esta tendencia. (Mwikirize et al., 2010)

Los laboratorios se pueden administrar en cualquiera de las tres formas: laboratorios convencionales donde los estudiantes e investigadores tienen acceso práctico al equipo, laboratorios virtuales que implican simulaciones y laboratorios en línea, donde usuarios operan y controlan el equipo físico de forma remota a través de un interfaz de usuario adecuada. (Fen & Sabri, 2014)

En teoría, un laboratorio virtual según Andújar & Mateo, (2010; Balamuralithara & Woods, (2009) podría ofrecer la experiencia de aprendizaje de un laboratorio físico, pero sin limitaciones, como el tiempo, la ubicación, el material y el equipo. Los laboratorios virtuales ofrecen muchas ventajas sobre los laboratorios convencionales. El tiempo es posiblemente la mayor ventaja de los laboratorios virtuales. Otra ventaja es que utilizan equipos virtuales. El equipo real envejece, se descompone, ocupa espacio, debe mantenerse y puede ser costoso y peligroso. (Yang-Mei & Bo, 2014)

Se pueden desarrollar laboratorios virtuales para ofrecer todas estas ventajas sin disminuir la experiencia del laboratorio. Existen muchas

soluciones comerciales basadas en simulaciones por computadora que responden a las necesidades del aprendizaje a distancia en muchas disciplinas. Se ha realizado un análisis de los productos existentes en el mercado. Se ha demostrado que, en la mayoría de los casos, estos productos han sido desarrollados por universidades para aplicaciones específicas y con beneficios limitados desde el punto de vista de los cálculos, el formato de gráficos y la interfaz de usuario. (Eliyaz et al., 2017)

### 1.2. Objetivo General.

Desarrollo de aplicaciones prácticas de sistemas combinatoriales de compuertas digitales utilizando instrumentación virtual LabVIEW

### 1.3. Objetivos Específicos.

- a. Describir los aspectos teóricos de la herramienta de simulación

LabVIEW aplicadas a los sistemas digitales.

- b. Diseñar las aplicaciones prácticas de sistemas combinatoriales utilizando instrumentos virtuales de NI LabVIEW.

- c. Analizar las aplicaciones desarrolladas en LabVIEW sobre NI Elvis III. .

## Capítulo 2: Fundamentación teórica.

#### 2.1. Introducción del uso de herramientas de simulación.

Uno de los principales enfoques de las Carreras de Telecomunicaciones, Electricidad y Electrónica de la Facultad de Educación Técnica para el Desarrollo en la Universidad Católica de Santiago de Guayaquil (UCSG) es proporcionar a cada graduado la capacidad de diseñar productos y sistemas de hardware y software utilizando conjuntos de herramientas de grado industrial.

El uso de estas herramientas para desarrollar sistemas integrados de adquisición y control de datos comienza con los primeros cursos técnicos a nivel de cuarto semestre. Los planes de estudio buscan exponer a los estudiantes a una amplia gama de lenguajes de software (ensamblador, C y orientado a objetos), así como proporcionar experiencia en la utilización de múltiples plataformas de desarrollo de microcontroladores.

Recientemente, los programas, mediante la incorporación de la tecnología de matriz de puerta programable en campo (FPGA) en su conjunto de hardware y lenguajes de descripción de hardware (específicamente VHDL) en sus lenguajes de programación. La intención fue proporcionar a los estudiantes un espectro de tecnologías de hardware y lenguajes de programación para elegir en la implementación de sus proyectos de diseño durante sus últimos semestres de clases.

Aunque, desde hace un tiempo atrás el entorno de programación gráfica LabVIEW FPGA no era intuitivo e insuficiente para enseñar lógica digital en la asignatura de Sistemas Digitales o Electrónica Digital. Sin embargo, el entorno de programación podría aumentarse con un juego de herramientas que permitiría a los estudiantes diseñar circuitos digitales utilizando iconos de dispositivos y luego compilar estos circuitos para descargarlos directamente al equipo Elvis III y a la placa FPGA Xilinx. En el semestre B-2018, UCSG financió un proyecto de desarrollo curricular mediante la herramienta de simulación LabVIEW que cumple con los requisitos del curso de diseño de

lógica digital y proporcionaría un mejor base de comprensión para los estudiantes de las carreras ya mencionadas.

En las siguientes secciones se describirán las herramientas básicas para análisis de sistemas digitales que tiene la plataforma de simulación de instrumentos virtuales LabVIEW

#### 2.2. Kit de herramientas basado en VHDL.

Al comenzar este proyecto, se reconoció rápidamente que, si bien los estudiantes en los cursos introductorios deben trabajar en el nivel de compuertas para darse cuenta de los fundamentos del diseño digital, en los cursos posteriores, tendrían que migrar rápidamente a el uso de lenguajes de descripción de hardware (HDL) para aprovechar al máximo el potencial de sus dispositivos FPGA.

Por esta razón, se decidió que, a través del entorno de desarrollo de LabVIEW, los estudiantes deberían diseñar gráficamente sus circuitos, pero también tener la capacidad de ver el equivalente HDL de los dispositivos que estaban usando. Por lo tanto, cada dispositivo en la biblioteca tenía que permitir a los estudiantes profundizar y ver la implementación en VHDL.

Por lo tanto, la Biblioteca Digital Logic VI aprovecha el nodo de interfaz HDL de LabVIEW FPGA. El nodo de interfaz HDL brinda la capacidad de utilizar código VHDL en lugar de código LabVIEW dentro de una FPGA VI. Para interactuar adecuadamente con el flujo de datos de LabVIEW, el nodo de interfaz HDL se define a través de su cuadro de diálogo de propiedades.

Las entradas y salidas se definen y configuran en la pestaña de parámetros y el módulo se define en VHDL en la pestaña código, tal como se muestra en la figura 2.1. El uso de esta metodología permite al estudiante interesado "profundizar" en cada dispositivo digital y ver cómo está implementado en VHDL. Por lo tanto, en la clase introductoria, pueden diseñar sistemas gráficamente y comenzar a aprender VHDL al mismo tiempo.

Figura 2. 1: Instrumento virtual del nodo de interfaz HDL. Elaborado por: Autor.

Debido a que los estudiantes utilizan una interfaz gráfica, la representación icónica de los dispositivos digitales es tan importante como su funcionalidad. Si bien los desarrolladores pueden crear iconos para representar sus VIs utilizando el editor de iconos incorporado, la necesidad de flexibilidad y capacidades avanzadas determinaron el uso de Microsoft Visio, que incluye efectos de imagen y admite gráficos vectoriales escalables. Para la Biblioteca Digital Logic VI, cada dispositivo recibe un icono apropiado que transmite su funcionalidad.

Los colores se utilizan para distinguir una familia de dispositivos de otra: los dispositivos combinatorios son amarillos y los dispositivos lógicos secuenciales son de color naranja. Después de crear los íconos en forma grande, GIMP se utilizó para agregar una sombra paralela y cambiar el tamaño a una imagen de 32x32 píxeles antes de importar al editor de íconos de LabVIEW.

Utilizando estas técnicas, cada dispositivo tiene plena funcionalidad. Por ejemplo, el dispositivo de contador bidireccional tiene un conjunto completo de controles y señales de salida que incluyen carga síncrona, reinicio asíncrono y conteo de terminales. Aunque la huella de este dispositivo es más grande que un simple dispositivo contador, los estudiantes se benefician más de tener estas E/S disponibles y aprender sus funciones.

Además, la mayoría de los VIs de lógica digital son polimórficos, lo que le permite al estudiante cambiar fácilmente el tamaño y el tipo de dispositivo, tal como se muestra en la figura 2.2. Al utilizar VIs polimórficos y dar total funcionalidad a cada dispositivo, los estudiantes tienen la ventaja de utilizar

una biblioteca conveniente de menos dispositivos funcionales en lugar de una biblioteca difícil de manejar con una lista exhaustiva de dispositivos.

Figura 2. 2: Estructura de VIs polimórficos. Fuente:

#### 2.3. Desarrollo de herramientas en NI LabVIEW.

La Biblioteca Digital Logic VI contiene un conjunto completo de dispositivos lógicos necesarios para desarrollar tareas/proyectos de laboratorio para un curso introductorio de lógica digital que incluye compuertas lógicas básicas, dispositivos combinatorios, dispositivos lógicos secuenciales y otros dispositivos de soporte general. Los dispositivos basados en HDL se representan como símbolos lógicos apropiados para dar la apariencia de un esquema de lógica digital durante el diseño.

Como se discutió anteriormente, la implementación de todos los dispositivos se realizó asumiendo que la placa de inicio Xilinx Spartan-3E es el objetivo FPGA y el reloj integrado (50 MHz, ciclo de trabajo del 50%) como el reloj base FPGA.

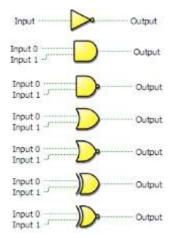

#### 2.3.1. Compuertas lógicas básicas en LabVIEW.

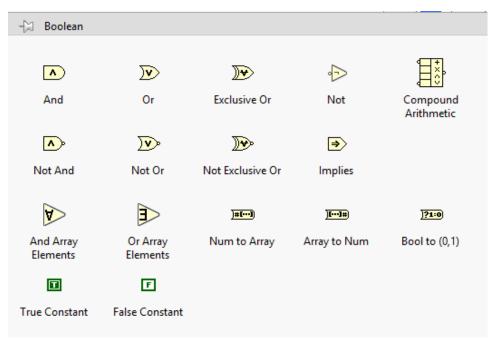

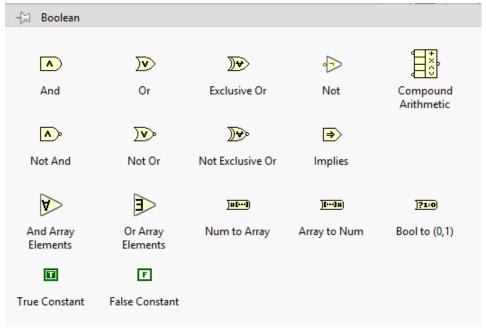

Las compuertas lógicas básicas son completas y están disponibles en varios tamaños. Las puertas lógicas con menos de cinco entradas tienen entradas de bits individuales como se muestra en la figura 2.3. De lo contrario,

las puertas lógicas tienen entradas de bus y los bits individuales deben tener acceso con un dispositivo de bus. (Suwannakhun & Tanitteerapan, 2017)

Figura 2. 3: Instrumentos de compuertas lógicas en LabVIEW. Elaborado por: Autor.

### 2.3.2. Dispositivos combinatorios en LabVIEW.

Los dispositivos combinatorios contenidos en la última versión de la biblioteca incluyen multiplexores, decodificadores / demultiplexores de línea, codificadores de prioridad, cambiadores lógicos, sumadores y comparadores de magnitud. Cada dispositivo combinatorio viene en diferentes tamaños como se muestra en la última columna de la figura 2.4.

Figura 2. 4: Instrumentos de dispositivos combinatoriales en LabVIEW. Elaborado por: Autor.

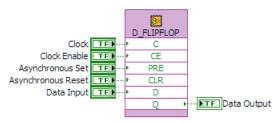

# 2.3.3. Dispositivos secuenciales.

Los dispositivos secuenciales incluyen Flip-Flops, registros y contadores. Al igual que los dispositivos combinatoriales, los dispositivos de registros y contadores vienen en diferentes tamaños. Además, el dispositivo Flip-Flop puede configurarse como un tipo D, T o J-K, tal como se muestra en la figura 2.5.

Figura 2. 5: Instrumentos de dispositivos secuenciales en LabVIEW. Elaborado por: Autor.

## Capítulo 3: Diseño y análisis de resultados

## 3.1. Descripción general del componente práctico.

El software LabVIEW que se utiliza ha sido desarrollado por National Instruments, y es un lenguaje de programación basado en íconos o también conocidos instrumentos virtuales (VI). Esto significa que, en lugar de programar con palabras como es la norma, el usuario programa soltando un instrumento virtual en la pantalla y "conectándolo" a otros VIs. Esto lo convierte en la plataforma perfecta para aprender a utilizar las compuertas lógicas tratadas en la asignatura de Electrónica Digital o Sistemas Digitales necesarias en la formación de ingenieros en Telecomunicaciones, Electricidad y Electrónica.

Para la experiencia práctica con las compuertas AND, OR, NOT, XOR, NAND, NOR y XNOR, la mayoría de los cursos de electrónica digital utilizan una rejilla plástica de agujeros (llamado Protoboard) con un patrón de conductores debajo de la rejilla para crear circuitos digitales. Se pueden insertar pequeños circuitos integrados (chips de plástico con patas de metal que contienen compuertas lógicas) en esta rejilla, luego las patas metálicas se pueden conectar a las patas metálicas de otros circuitos integrados utilizando un cable telefónico para crear una realización física de un circuito digital. Estás perdiendo algunas oportunidades cuando no tienes la experiencia de conectar los circuitos digitales reales.

LabVIEW le permite al usuario crear estos circuitos utilizando un diagrama de control y una interfaz de usuario que es familiar para cualquier usuario de Microsoft Windows o Mac O/S sin tener que perder tiempo en meterse con cables, fuentes de alimentación y otros. Otro beneficio de utilizar LabVIEW son las herramientas de interfaz de usuario altamente desarrolladas. Por ejemplo, el panel frontal del equipo electrónico más complejo se puede desarrollar con componentes simples de arrastrar y soltar. Se puede desarrollar una interfaz con entradas como interruptores, botones, perillas, controles deslizantes, entradas de texto o numéricas, etc. Las opciones de salida también tienen una amplia gama que incluye gráficos, LED

(pequeñas luces de colores por falta de una mejor explicación), pantalla tipo texto o numérico, indicadores analógicos, etc.

### 3.2. Descripción general de LabVIEW.

En esta sección se describe brevemente la funcionalidad de la plataforma de simulación LabVIEW. En LabVIEW, los modelos desarrollados para una solución de un problema matemático o lógico dado usando la programación gráfica se conocen como VIs y cada VI utiliza varias funciones que manipulan y mapean la entrada del usuario final y muestran esa información, la mueven a otros archivos u otras computadoras. Para trabajar con LabVIEW, primero, abra la versión de LabVIEW y cree un proyecto para su trabajo, tal como se muestra en la figura 3.1.

Figura 3. 1: Ventana principal del software LabVIEW 2018. Elaborado por: Autor.

Cada bloque VI contiene los tres componentes:

### 3.2.1. Panel frontal

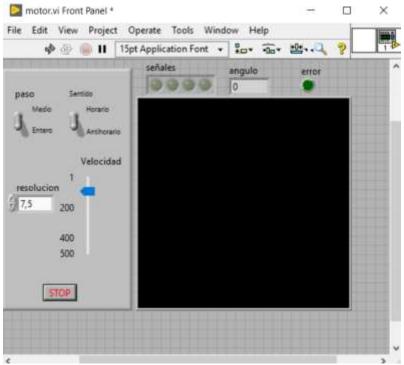

En la figura 3.2 muestra un ejemplo de panel frontal en la que se observan varios elementos, tales como puntero vertical slide, conversión booleana, de cadenas y rutas, lista de tablas y gráficos, contenedores variantes de E/S, entre otras.

Figura 3. 2: Ventana de trabajo del panel frontal en LabVIEW. Elaborado por: Autor.

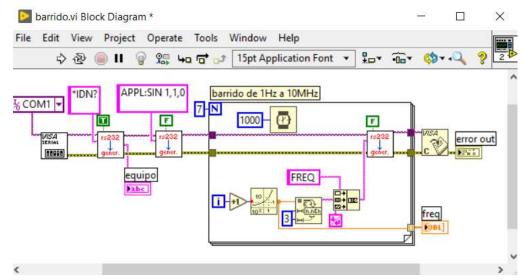

#### 3.2.2. Panel de bloque

Contiene código fuente gráfico para describir la funcionalidad del VI. Los objetos del panel frontal aparecen como terminales en el diagrama de bloques, tal como se muestra en la figura 3.3. El diagrama de bloques comprende estructuras, matriz, clúster, numérico, booleano, comparación de cadenas, temporización, diálogo y uso, E/S de archivo, aplicación de forma de onda, sincronización, gráficos, entre otras.

#### 3.2.3. Panel de iconos y conectores.

Se puede usar para identificar el VI de modo que se pueda usar otro VI (sub-VI) en VI. El rol Sub VI es similar a la subrutina en los lenguajes de programación G basados en texto [6]. LabVIEW tiene un gran alcance en diversas áreas, para cerrar la brecha entre las teorías y su implementación práctica. LabVIEW se utiliza principalmente en la interfaz de adquisición de datos con hardware. El dominio y el tipo de uso de la plataforma virtual LabVIEW, tal como se muestra en la figura 3.4.

Figura 3. 3: Conexión de la antena al equipo Elvis III de NI. Elaborado por: Autor.

Figura 3. 4: Conexión de la antena al equipo Elvis III de NI. Elaborado por: Autor.

# 3.3. Desarrollo de aplicaciones prácticas de circuitos combinatoriales en LabVIEW.

En esta sección se desarrollan las aplicaciones prácticas experimentales para la asignatura de sistemas digitales.

### 3.3.1. Escenario práctico 1: Aplicación de compuertas lógicas.

En esta sección se realiza la práctica de compuertas lógicas mediante el empleo de herramientas de simulación de LabVIEW. A continuación, se realiza la explicación de los pasos a seguir para el desarrollo completo de la aplicación práctica que servirá de ayuda a la asignatura de Sistemas Digitales.

### Paso 1: Configuraciones previas a la práctica.

Hay que asegurar que el equipo esté conectado a la fuente de alimentación de 24 voltios continuos. Después se debe realizar la conexión de la antena wifi al dispositivo, tal como se muestra en la figura 3.5.

Figura 3. 5: Conexión de la antena al equipo Elvis III de NI. Elaborado por: Autor.

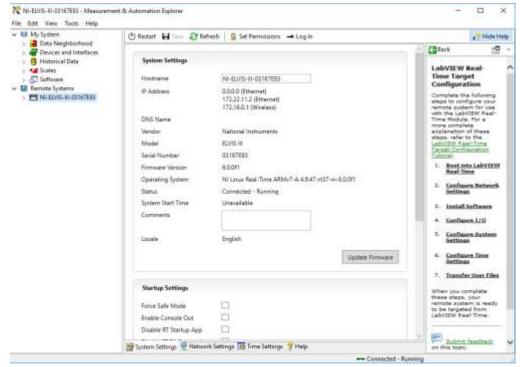

# Paso 2: Configuraciones la red inalámbrica en Elvis III de National Instruments.

Al momento de conectar el equipo vía USB se abrirá una ventana emergente, tal como se muestra en la figura 3.6. Después se procede a seleccionar la configuración e instalación del software (véase la figura 3.7) NI Elvis III para lo cual se abre la herramientas Ni Max que sirve para configurar los dispositivos de la familia de National Instruments.

Figura 3. 6: Ventana de configuración de dispositivos detectados en NI Elvis III. Elaborado por: Autor.

Figura 3. 7: Ventana de instalación del software NI Elvis III. Elaborado por: Autor.

La figura 3.8 y figura 3.9 muestra la herramienta que permitirá al equipo NI Elvis III realizar las respectivas configuraciones a los equipos a una red alámbrica o inalámbrica.

Figura 3. 8: Ventana de configuración para redes de NI Elvis III. Elaborado por: Autor.

Figura 3. 9: Ventana de configuración de adaptadores de redes de NI Elvis III. Elaborado por: Autor.

En configuraciones ir a Wireless adapter WLAN y seleccionar crear una red WLAN para así poder configurar el nombre de la red, tal como se muestra en la figura 3.10.

Figura 3. 10: Ventana de configuración del adaptador WLAN de NI Elvis III. Elaborado por: Autor.

Al guardar las configuraciones se visualiza la red creada y se procede a realizar la respectiva conexión a la red, tal como se muestra en la figura 3.11.

Figura 3. 11: Selección de la red NI\_ELVIS\_WIFI. Elaborado por: Autor.

# Paso 3: Creación de proyecto en el Elvis III con LabVIEW.

Después de abrir el programa LabVIEW, se procede a la creación de un nuevo proyecto al dar clic en Create New Project, tal como se muestra en la figura 3.12.

Figura 3. 12: Creación de un nuevo proyecto en LabVIEW. Elaborado por: Autor.

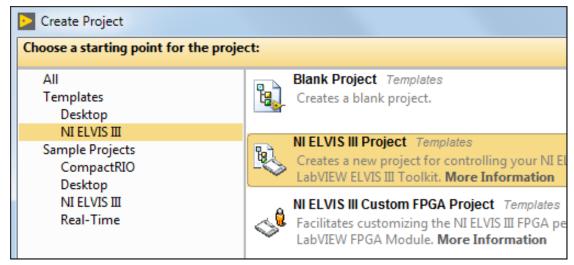

Después, se procede a seleccionar en Plantillas» **NI ELVIS III** y N**I ELVIS III Project** de la lista de proyectos, tal como se muestra en la figura 3.13.

Figura 3. 13: Elección del tipo de proyecto mediante NI ELVIS III. Elaborado por: Autor.

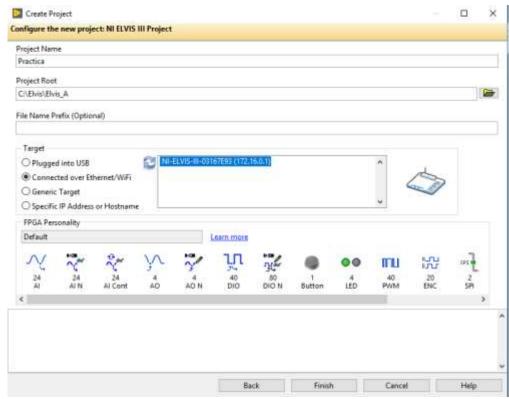

La figura 3.14 muestra como seleccionar la ubicación del archivo a conectar y el modo de conexión a escoger es WiFi. Al crear el proyecto se crea una ventana de exploración en la cual se podrá acceder a todas las herramientas y el VI principal, tal como se muestra en la figura 3.15.

Figura 3. 14: Configuración de un nuevo proyecto en LabVIEW para conectar a WiFi.

Elaborado por: Autor.

Figura 3. 15: Creación de un nuevo proyecto en LabVIEW. Elaborado por: Autor.

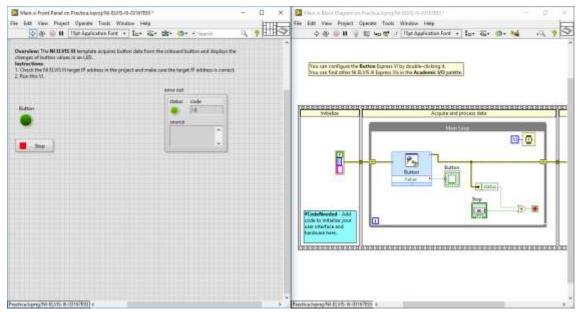

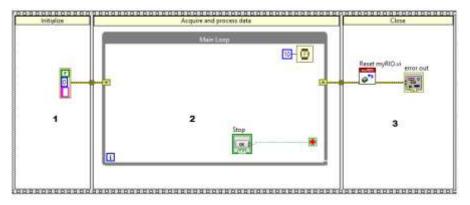

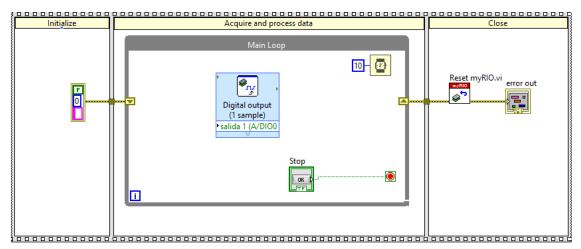

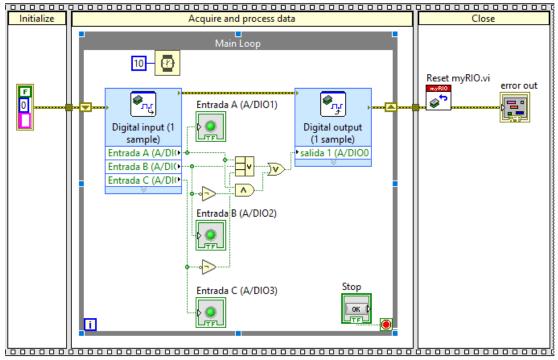

El archivo main o archivo principal de ejecución con formato VI, o instrumento virtual que consta de dos ventanas una el panel de control y otra el bloque de diagrama, tal como se muestra en la figura 3.16.

Figura 3. 16: Ventanas del panel de control y bloque de diagrama para la primera aplicación práctica.

Elaborado por: Autor.

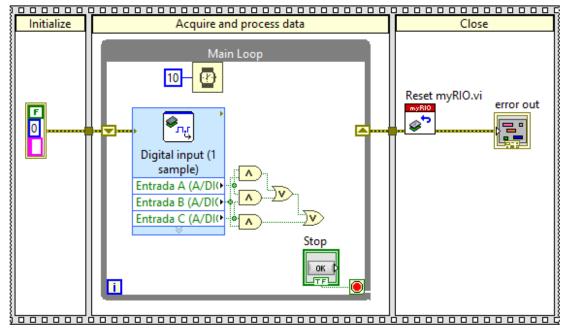

El bloque de diagrama ya consta con una condición inicial (véase la figura 3.17) donde realiza la lectura de un valor digital mediante el botón en el Elvis III, se procede a dejar el archivo en blanco para continuar.

Figura 3. 17: Establecer la lectura de un valor digital mediante el botón Elvis III. Elaborado por: Autor.

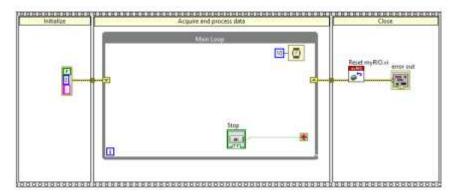

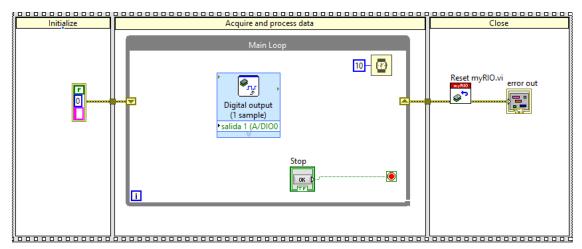

La figura 3.18 muestra la forma de ejecución que será dividida en tres procesos mediante un flat secuencia el cual tendrá: (1) la inicialización de las variables, (2) la adquisición donde estará un bucle while en el cual se va a programar, y (3) para cerrar el puerto de la tarjeta y entre en reposo.

Figura 3. 18: Ejecución de un flat secuencial en tres procesos. Elaborado por: Autor.

# Paso 4: Definición de problema con un circuito de conmutación mediante lógica binaria.

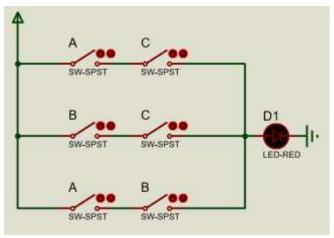

En la práctica 1 se define el siguiente circuito digital topológico en el cual tendrá tres entradas a, b, c y una salida, tal como se muestra en la figura 3.19.

Figura 3. 19: Circuito de conmutación mediante lógica binaria. Elaborado por: Autor.

La tabla de verdad resultante del circuito es:

| Α | В | С | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Donde la función que gobierna el circuito es,

$$S = BC + AC + AB$$

Para el problema es necesario agregar tres entradas y una salida digitales.

# Paso 5: Adquisición y generación de señales digitales mediante Elvis III.

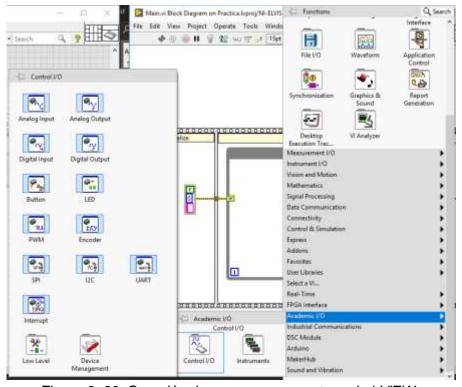

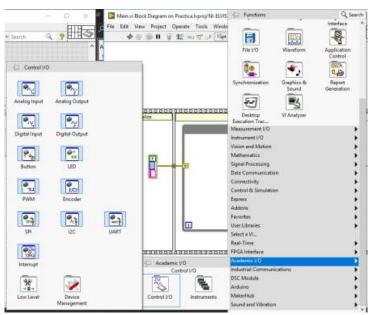

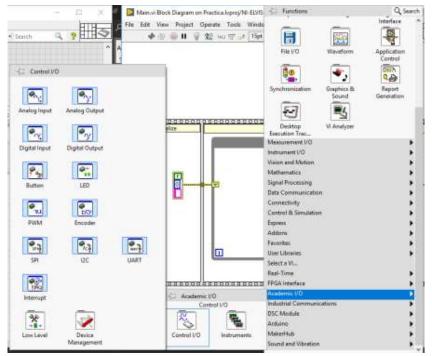

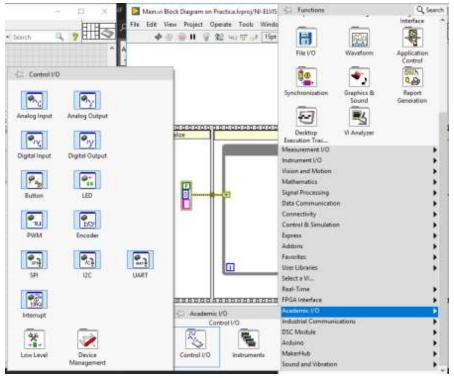

Dar clic en el bloque de diagrama, después ir a Academic l/O, control l/O y seleccionar Digital Output la cual sirve para escribir un dato digital mediante el controlador de la Elvis III, tal como se muestra en la figura 3.20.

Figura 3. 20: Creación de un nuevo proyecto en LabVIEW. Elaborado por: Autor.

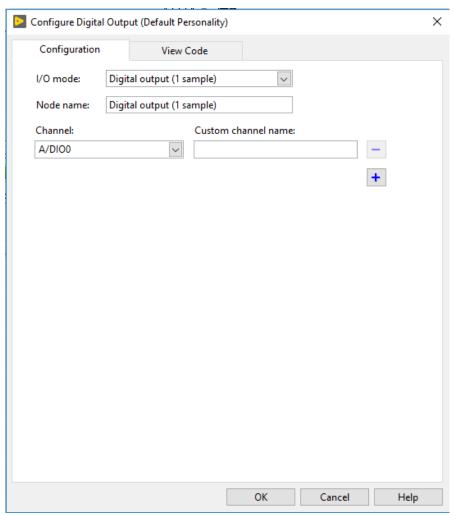

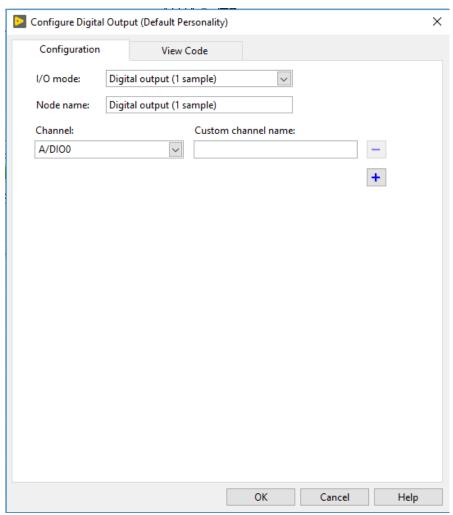

Al crear la salida digital se abre una ventana emergente de configuración (véase la figura 3.21) donde se va a configurar el canal de adquisición con su respectivo puerto (la tarjeta Elvis tiene dos puertos a y b cada uno tiene 20 entradas o salidas digitales). Al crear el bloque de salida digital es necesario incrustarle en el lazo principal de ejecución (véase la figura 3.22) que sirve como salida del problema definido.

Figura 3. 21: Configuración de salidas digitales para la aplicación práctica 1. Elaborado por: Autor.

Figura 3. 22: Bloque de diagrama con las salidas digitales incorporadas para esta práctica 1.

Elaborado por: Autor.

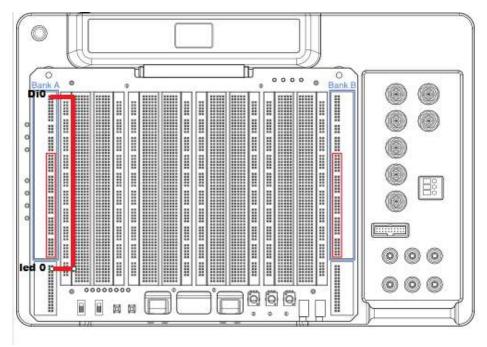

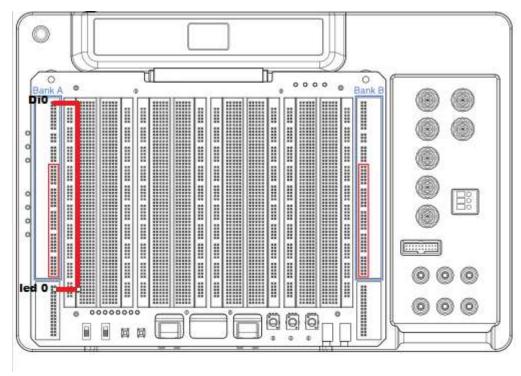

La figura 3.23 muestra las conexiones físicas en la placa Elvis III.

Figura 3. 23: Conexiones de salidas digitales en la Elvis III para práctica 1. Elaborado por: Autor.

Después, se procede a agregar las entradas digitales (véase la figura 3.24) para el sistema ir a bloque de diagrama Academic VO >> control VO>> digital input

Figura 3. 24: Creación de controles de entrada/salida (I/O) para práctica 1. Elaborado por: Autor.

Después, se procede a configurar las entradas digitales, para lo cual se abre una ventana emergente donde se procede a configurar los pines de entrada en la tarjeta Elvis III, tal como se muestra en la figura 3.25.

Figura 3. 25: Configuración de entradas digitales para la aplicación práctica 1. Elaborado por: Autor.

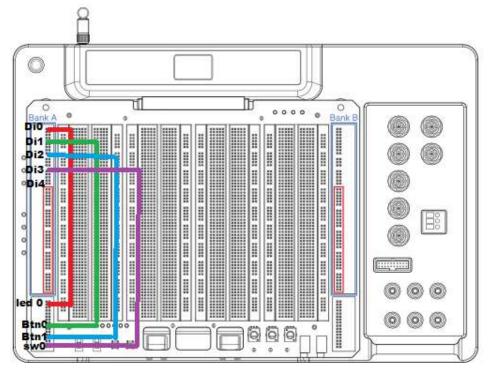

Después, de las configuraciones de entradas y salidas digitales se procede a las conexiones físicas que se muestran en la figura 3.26.

Figura 3. 26: Conexiones de entradas digitales en la Elvis III para práctica 1. Elaborado por: Autor.

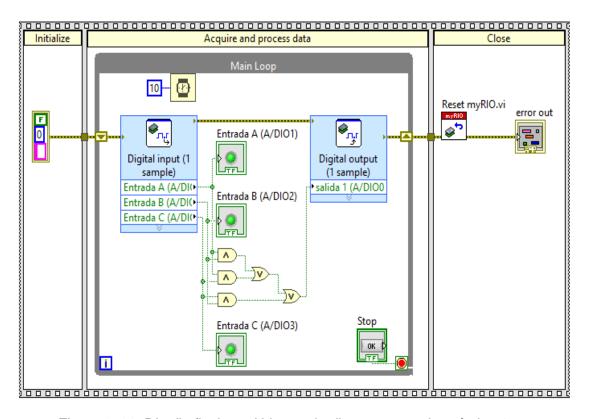

Se procede a conectar el bloque de control del Elvis III en el bloque de diagrama y realizar la lógica de la función S = BC + AC + AB utilizando los bloques lógicos que se muestran en la figura 3.27.

Figura 3. 27: Instrumentos virtuales booleanos para la función S de la práctica 1. Elaborado por: Autor.

En la figura 3.28 se procede a agregar tres bloques de multiplicación (compuertas AND), y dos bloques de suma (compuertas OR).

Figura 3. 28: Bloque de diagrama con el diseño de la función lógica digital. Elaborado por: Autor.

Finalmente, la figura 3.29 muestra la conexión de la función de salida con el bloque de salida digital.

Figura 3. 29: Diseño final en el bloque de diagrama para la práctica 1. Elaborado por: Autor.

### 3.3.2. Escenario práctico 2: Aplicación de lógica combinatorial.

En la practica 2 se define el siguiente circuito en el cual tendrá tres entradas a, b, c y una salida correspondiente a la tabla de verdad. La tabla de verdad resultante del circuito es:

| В | С                          | S                                             |

|---|----------------------------|-----------------------------------------------|

| 0 | 0                          | 0                                             |

| 0 | 1                          | 0                                             |

| 1 | 0                          | 0                                             |

| 1 | 1                          | 0                                             |

| 0 | 0                          | 1                                             |

| 0 | 1                          | 1                                             |

| 1 | 0                          | 1                                             |

| 1 | 1                          | 0                                             |

|   | 0<br>0<br>1<br>1<br>0<br>0 | 0 0<br>0 1<br>1 0<br>1 1<br>0 0<br>0 1<br>1 0 |

La resolución mediante aplicación de algebra booleana y aplicando teoremas de reducción, la función que gobierna el circuito es,

$$S = AB' + ABC'$$

Para el problema es necesario agregar tres entradas y una salida digitales. Dar clic en el bloque de diagrama, ir a Academic VO, Control VO y seleccionar Digital Output la cual sirve para escribir un dato digital mediante el controlador de la Elvis III, tal como se muestra en la figura 3.30.

Figura 3. 30: Creación de controles de entrada/salida (I/O) para práctica 2. Elaborado por: Autor.

Al crear la salida digital se abre una ventana emergente de configuración (ver figura 3.31) donde se configura el canal de adquisición con su respectivo puerto (la tarjeta Elvis tiene dos puertos a y b cada uno tiene 20 entradas o salidas digitales).

Al crear el bloque de salida digital es necesario incrustarle en el lazo principal de ejecución que sirve como salida del problema definido, tal como se muestra en la figura 3.32.

Figura 3. 31: Configuración de salidas digitales para la aplicación práctica 2. Elaborado por: Autor.

Figura 3. 32: Bloque de diagrama con las salidas digitales incorporadas para esta práctica 2.

Elaborado por: Autor.

Las conexiones físicas de la salida digital se muestran en la figura 3.33.

Figura 3. 33: Conexiones de salidas digitales en la Elvis III para práctica 2. Elaborado por: Autor.

La figura 3.34 muestra el procedimiento para agregar las entradas digitales para el sistema, ir a bloque de diagrama Academic VO >> Control VO>> digital input.

Figura 3. 34: Creación de un nuevo proyecto en LabVIEW. Elaborado por: Autor.

Se abre una ventana emergente donde se procede a configurar los pines de entrada en la tarjeta Elvis III, tal como se muestra en la figura 3.35.

Figura 3. 35: Configuración de entradas digitales para la aplicación práctica 2. Elaborado por: Autor.

La figura 3.36 muestra las conexiones físicas de las entradas digitales.

Figura 3. 36: Conexiones de entradas digitales en la Elvis III para práctica 2. Elaborado por: Autor.

Se procede a conectar el bloque de control del Elvis III en el bloque de diagrama y realizar la lógica de la función S = AB' + ABC' utilizando los bloques lógicos (ver figura 3.37) en el bloque de diagrama.

Figura 3. 37: Instrumentos virtuales booleanos para la función S de la práctica 2. Elaborado por: Autor.

Finalmente, en la figura 3.38 se agregan los tres bloques de multiplicación (compuertas AND), dos bloques de suma (compuertas OR)

Figura 3. 38: Diseño final en el bloque de diagrama para la práctica 2. Elaborado por: Autor.

## 3.4. Resultados obtenidos de las dos prácticas diseñadas.

En esta sección se muestran los resultados obtenidos de las dos aplicaciones prácticas diseñadas en la sección 3,3. Las figuras 3.39 a 3.42 muestran las entradas (A, B y C) y la salida (S) para la función S = BC + AC + AB. La figura 3.39 muestra que cuando A=0, B=C=1, la salida S=1 (ver tabla de verdad de la aplicación práctica 1).

Figura 3. 39: Resultado obtenido en la práctica 1 cuando A=0 y B=C=1. Elaborado por: Autor.

En la figura 3.40 se muestra el resultado obtenido para la misma función que se obtuvo en la figura 3.39 pero las variables de entrada toman los siguientes valores binarios, A=C=1 y B=0, para que su salida sea verdadera.

Figura 3. 40: Resultado obtenido en la práctica 1 cuando A=0 y B=C=1. Elaborado por: Autor.

En la figura 3.41 se muestra el resultado obtenido pero las variables de entrada toman los siguientes valores binarios, A=B=1 y C=0, para que su salida sea verdadera.

Figura 3. 41: Resultado obtenido en la práctica 1 cuando A=B=0 y B. Elaborado por: Autor.

En la figura 3.42 se muestra el resultado obtenido pero las variables de entrada toman los siguientes valores binarios, A=B=C=1, para que su salida sea verdadera.

Figura 3. 42: Resultado obtenido en la práctica 1 cuando A=B=C=1. Elaborado por: Autor.

Después, se muestran las figuras 3.43 a 3.45 los resultados obtenidos de las dos aplicaciones prácticas diseñadas en la sección 3,3. Las figuras 3.43 a 3.45 muestran las entradas (A, B y C) y la salida (S) para la función S = AB' + ABC'. La figura 3.44 muestra que cuando A=1, B=C=0, la salida S=1 (ver tabla de verdad de la aplicación práctica 2). Similar, la figura 3.44 muestra la salida para cuando A=C=1 y (S). La figura 3.43 muestra el resultado si A=B=1 y la

Figura 3. 43: Resultado obtenido en la práctica 2 cuando A=1 y B=C=0. Elaborado por: Autor.

Figura 3. 44: Resultado obtenido en la práctica 2 cuando A=B=C=1. Elaborado por: Autor.

Figura 3. 45: Resultado obtenido en la práctica 2 cuando A=B=1, C=0. Elaborado por: Autor.

#### Conclusiones

La tecnología informática y de comunicación ha tenido un impacto significativo en el sistema educativo de ingeniería. Esta tecnología ha mejorado el aprendizaje en línea y colaborativo. Además de eso, mejora las experiencias de aprendizaje de los estudiantes. Uno de los elementos distintivos de la educación en ingeniería es el requisito de laboratorio.

En un curso introductorio como el diseño digital, los estudiantes están siendo sometidos a un número significativo de nuevas ideas y procesos. Con el fin de reforzar la experiencia de aprendizaje en el aula, los estudiantes deben poder, de manera directa, la transición del diseño de pizarra a un circuito de trabajo de una manera altamente eficiente e intuitiva. Pasar tiempo insertando chips en protoboards y conectando una gran cantidad de cables a pines no es eficiente y tiene un nivel de abstracción que reduce el aprendizaje conceptual.

Mediante el uso del nuevo kit de herramientas de diseño digital de LabVIEW, los estudiantes pueden traducir fácilmente los circuitos lógicos combinatorios y secuenciales que tratan en este trabajo a un diseño en su computadora. Una vez que se completa el diseño, los estudiantes pueden descargarlo rápidamente a la placa de desarrollo basada en NI Elvis III y/o una FPGA para pruebas y depuración.

### Recomendaciones.

Realizar proyectos relacionados con los circuitos Flip-Flop y su implementación híbrida sobre LabVIEW y MatLab.

Desarrollar un aprendizaje centrado en el alumno, para crear el interés en el modelado de circuitos y sistemas digitales ya sea a nivel de pregrado y posgrado.

### Bibliografía.

- Amer, M. A., Cortina-Puig, M., Martinez, V., Cruz, J., & Morral, J. (2015).

Implementation of a LabVIEW-based virtual laboratory. 2015 IEEE

International Conference on Industrial Technology (ICIT), 3274–3277.

https://doi.org/10.1109/ICIT.2015.7125583

- Andújar, J. M., & Mateo, T. J. (2010). Diseño de Laboratorios Virtuales y/o Remotos. Un Caso Práctico. *Revista Iberoamericana de Automática e Informática Industrial*, 7(1), 64–72. https://doi.org/10.4995/RIAI.2010.01.06

- Balamuralithara, B., & Woods, P. C. (2009). Virtual laboratories in engineering education: The simulation lab and remote lab. *Computer Applications in Engineering Education*, 17(1), 108–118. https://doi.org/10.1002/cae.20186

- Eliyaz, M., Nagaraju, N., & Madhu, N. (2017). Implementation of Number Base Conversions using LabVIEW. *IOSR Journal of Electronics and Communication Engineering*, 12(03), 75–80. https://doi.org/10.9790/2834-1203047580

- Fen, Y. W., & Sabri, L. A.-H. M. (2014). Integration of LabVIEW for Novel Interactive Learning Courseware on Digital Electronics. *International Journal for Innovation Education and Research*, *2*(11), 156–163.

- Mwikirize, C., Tumusiime, A. A., Musasizi, P. I., Tickodri-Togboa, S. S., Katumba, A., & Butime, J. (2010). New Dimensions in Teaching Digital Electronics: A Multimode Laboratory Utilizing NI ELVIS IITM, LabVIEW and NI Multisim. *International Journal of Online Engineering (iJOE)*, 6(4), 49–54. https://doi.org/10.3991/ijoe.v6i4.1396

- Suwannakhun, S., & Tanitteerapan, T. (2017). Design and Development of Distance Laboratory Package for Teaching Basic Electronics via Cloud

Computing. *International Journal of Online Engineering (iJOE)*, 13(08), 60. https://doi.org/10.3991/ijoe.v13i08.6985

Yang-Mei, L., & Bo, C. (2014). Electronic Circuit Virtual Laboratory Based on LabVIEW and Multisim. 2014 7th International Conference on Intelligent Computation Technology and Automation, 222–225. https://doi.org/10.1109/ICICTA.2014.61

# **DECLARACIÓN Y AUTORIZACIÓN**

Yo, PLAZA CALDERÓN, MARTIN FERNANDO con C.C: # 080238660-7 autor del Trabajo de examen complexivo: Desarrollo de aplicaciones prácticas de sistemas combinatoriales de compuertas digitales utilizando instrumentación virtual LabVIEW previo a la obtención del título de INGENIERO EN TELECOMUNICACIONES en la Universidad Católica de Santiago de Guayaquil.

- 1.- Declaro tener pleno conocimiento de la obligación que tienen las instituciones de educación superior, de conformidad con el Artículo 144 de la Ley Orgánica de Educación Superior, de entregar a la SENESCYT en formato digital una copia del referido trabajo de titulación para que sea integrado al Sistema Nacional de Información de la Educación Superior del Ecuador para su difusión pública respetando los derechos de autor.

- 2.- Autorizo a la SENESCYT a tener una copia del referido trabajo de titulación, con el propósito de generar un repositorio que democratice la información, respetando las políticas de propiedad intelectual vigentes.

Guayaquil, 6 de marzo del 2020

| f. |  |  |  |

|----|--|--|--|

|    |  |  |  |

Nombre: PLAZA CALDERÓN, MARTÍN FERNANDO

C.C: 080238660-7

#### REPOSITORIO NACIONAL EN CIENCIA Y TECNOLOGÍA FICHA DE REGISTRO DE TESIS/TRABAJO DE TITULACIÓN **TÍTULO Y SUBTÍTULO:** Desarrollo de aplicaciones prácticas de sistemas combinatoriales de compuertas digitales utilizando instrumentación LabVIEW. **AUTOR(ES)** Plaza Calderón, Martin Fernando REVISOR(ES)/TUTOR(ES) M. Sc. PACHECO BOHÓRQUEZ, HÉCTOR IGNACIO INSTITUCIÓN: Universidad Católica de Santiago de Guayaquil **FACULTAD:** Facultad de Educación Técnica para el Desarrollo **CARRERA:** Ingeniería en Telecomunicaciones **TITULO OBTENIDO:** Ingeniero en Telecomunicaciones No. DE PÁGINAS: FECHA DE PUBLICACIÓN: 6 de marzo del 2020 **ÁREAS TEMÁTICAS:** Sistemas Digitales, Instrumentación Virtual Instrumentos, Virtuales, Lógica, Secuencial, Combinatorial, **PALABRAS CLAVES/KEYWORDS:** Memoria

## RESUMEN/ABSTRACT:

El trabajo del componente práctico del examen complexivo trata del desarrollo de aplicaciones prácticas de sistemas combinatoriales de compuertas digitales utilizando instrumentación virtual LabVIEW de National Instruments, este desarrolló un juego de herramientas de diseño de lógica digital que se integró en el software y que permite a los estudiantes diseñar utilizando dispositivos lógicos combinatorios y secuenciales típicos que iban desde compuertas lógicas AND, OR, NOT, XOR, NAND, NOR, XNOR hasta los dispositivos Flip-Flops, contadores, comparadores, selectores, decodificadores, entre otros. La electrónica digital es la columna vertebral de la tecnología actual, juega un papel fundamental en el crecimiento de la humanidad. La memoria digital es parte de la electrónica digital y consiste en bloques de construcción de Flip-Flops diseñados mediante el uso de puertas lógicas NAND y NOR. La validación del almacenamiento de información en forma de bits puede entenderse a partir del análisis del funcionamiento de flip-flops. Finalmente, este proyecto permite disponer de una ayuda académica en la enseñanza de los sistemas digitales.

| ADJUNTO PDF:                    | ⊠ SI                                     | □ NO               |                      |  |  |  |

|---------------------------------|------------------------------------------|--------------------|----------------------|--|--|--|

| CONTACTO CON AUTOR/ES:          | <b>Teléfono:</b> +593-9-                 | E-mail: <u>mar</u> | tinplaza97@gmail.com |  |  |  |

|                                 | 968651014                                |                    |                      |  |  |  |

| CONTACTO CON LA INSTITUCIÓN:    | Nombre: Palacios Meléndez Edwin Fernando |                    |                      |  |  |  |

| COORDINADOR DEL PROCESO DE      | Teléfono: +593-9-67608298                |                    |                      |  |  |  |

| UTE                             | E-mail: edwin.palacios@cu.ucsg.edu.ec    |                    |                      |  |  |  |

| SECCIÓN PARA USO DE BIBLIOTECA  |                                          |                    |                      |  |  |  |

| Nº. DE REGISTRO (en base a dato | os):                                     |                    |                      |  |  |  |

| Nº. DE CLASIFICACIÓN:           |                                          |                    |                      |  |  |  |

| DIRECCIÓN URL (tesis en la web  | ):                                       |                    |                      |  |  |  |