SISTEMA DE POSGRADO

MAESTRÍA EN TELECOMUNICACIONES

#### TEMA:

Implementación de procesamiento de señales ECG mediante filtrado digital FIR utilizando el dispositivo programable FPGA

#### **AUTOR:**

Aguilar Jaramillo, José Manuel

Trabajo de Titulación previo a la obtención del Grado Académico de MAGÍSTER EN TELECOMUNICACIONES

TUTOR:

Palacios Meléndez, Edwin Fernando

Guayaquil, Ecuador

Guayaquil, 06 de Junio del 2017

## SISTEMA DE POSGRADO MAESTRÍA EN TELECOMUNICACIONES

#### CERTIFICACIÓN

Certificamos que el presente trabajo fue realizado en su totalidad por el Magíster **Aguilar Jaramillo, José Manuel** como requerimiento parcial para la obtención del Grado Académico de **MAGÍSTER EN TELECOMUNICACIONES**.

| TUTOR                             |

|-----------------------------------|

| Palacios Meléndez, Edwin Fernando |

| DIRECTOR DEL PROGRAMA             |

| Romero Paz, Manuel de Jesús       |

Guayaquil, a los 06 días del mes de junio del año 2017

SISTEMA DE POSGRADO

MAESTRÍA EN TELECOMUNICACIONES

#### **DECLARACIÓN DE RESPONSABILIDAD**

Yo, Aguilar Jaramillo, José Manuel

#### **DECLARÓ QUE:**

El Trabajo de Titulación "Implementación de procesamiento de señales ECG mediante filtrado digital FIR utilizando el dispositivo programable FPGA", previa a la obtención del grado Académico de Magíster en Telecomunicaciones, ha sido desarrollado, respetando derechos intelectuales de terceros conforme las citas que constan en el documento, cuyas fuentes se incorporan en las referencias o bibliografías. Consecuentemente este trabajo es de mi total autoría.

En virtud de esta declaración, me responsabilizó del contenido, veracidad y alcance científico del Trabajo de Titulación del Grado Académico en mención.

Guayaquil, a los 06 días del mes de junio del año 2017

Aguilar Jaramillo, José Manuel

**EL AUTOR**

SISTEMA DE POSGRADO

MAESTRÍA EN TELECOMUNICACIONES

#### **AUTORIZACIÓN**

Yo, Aguilar Jaramillo, José Manuel

Autorizó a la Universidad Católica de Santiago de Guayaquil, la publicación, en la biblioteca de la institución del Trabajo de Titulación de Maestría titulado: "Implementación de procesamiento de señales ECG mediante filtrado digital FIR utilizando el dispositivo programable FPGA", cuyo contenido, ideas y criterios son de mi exclusiva responsabilidad y total autoría.

Guayaquil, a los 06 días del mes de junio del año 2017

|    | EL AUTOR                      |  |

|----|-------------------------------|--|

|    |                               |  |

| Δ. | guilar Jaramillo, José Manuel |  |

#### REPORTE DE URKUND

#### Dedicatoria

Por medio de este trabajo de titulación la dedico A ti mi Dios, que me has dado la casualidad de vivir y de regalarme una familia maravillosa. Por brindarme la oportunidad de bendecirme por llegar hasta donde he llegado. Con mucho respeto a mis padres, que a pesar de todas las dificultades que vivimos siempre han estado conmigo apoyándome en mis estudios, dándome palabras de aliento y ánimo en todo momento.

Gracias a mis padres, por darme la mejor herencia que un padre de familia le puede dar a sus hijos, ahora con el estudio de cuarto nivel; el mismo complementa mi carrera universitaria, ya que es parte fundamental para mi futuro profesional, por todo esto les agradezco de todo corazón que estén conmigo a mi lado en todo momento, solamente les estoy devolviendo un poco de lo que ustedes me han venido dando desde un principio. Siempre dando lo mejor de mí para que se sientan orgullosos de mis logros y metas alcanzadas.

A mi hermana Estefany Alexandra y mis sobrinas: Dulce María y Domenica Stephania, a quienes aprecio y quiero mucho.

En especial a Damaris Samantha Granda Martínez por darme fuerzas incondicionales ya que ha estado en todo momento. Gracias a su apoyo con palabras de aliento cuando más lo necesite. "Nada es imposible cuando se retoma la fe en sí mismo".

#### **Agradecimientos**

MsC. Edwin Fernando Palacios Meléndez, quien fue mi tutor de tesis, por su asesoramiento y predisposición permanente en aclarar mis dudas y brindarme sugerencias en la redacción de la misma, por su enseñanza y más que todo por la amistad que se formó.

A todos los profesores que conformaron el grupo de docentes durante todo este tiempo, ya que gracias a los conocimientos adquiridos en la misma me han servido de mucho para implementar en el hábito laboral y profesional.

Son algunas personas que han formado parte de mi vida profesional a las cuales me encantaría agradecerles su amistad, consejos, apoyo, ánimo y compañía en los momentos más difíciles de mi vida, sin importar en donde estén quiero darles las gracias por formar parte de mi vida, por todo lo que me han brindado y por todas sus bendiciones.

A la Universidad Católica de Santiago de Guayaquil y su Facultad de Educación Técnica para el Desarrollo por darme la oportunidad de capacitarme y superarme, ya que las posibilidades de superación que se me han brindado son incomparables y antes de esto, nunca pensé que serían posibles que algún día llegaría a tenerlas.

De la misma manera, a mi compañero de Ingeniería y ahora en el estudio de masterado Gary Torres Villón por su valiosa amistad en estos estudios que han fortalecido nuestros lazos de amistad y compañerismo.

SISTEMA DE POSGRADO

MAESTRÍA EN TELECOMUNICACIONES

### TRIBUNAL DE SUSTENTACIÓN

| PALACIO | OS MELÉNDEZ, EDWIN FERNANDO  |

|---------|------------------------------|

|         | TUTOR                        |

|         |                              |

|         |                              |

| f       |                              |

|         | OVA RIVADENEIRA, LUIS SILVIO |

|         | REVISOR                      |

|         |                              |

|         |                              |

| f       |                              |

|         |                              |

| ZAMOI   | RA CEDEÑO, NESTOR ARMANDO    |

|         | REVISOR                      |

|         |                              |

|         |                              |

| f       |                              |

| RON     | MERO PAZ MANUEL DE JESÚS     |

VIII

DIRECTOR DEL PROGRAMA

### ÍNDICE GENERAL

| ÍNDICE  | DE           | FIGURAS                                    | XI   |

|---------|--------------|--------------------------------------------|------|

| ÍNDICE  | DE           | TABLAS                                     | XIII |

| Resum   | en           |                                            | XIV  |

| Abstrac | ct           |                                            | XV   |

|         |              |                                            |      |

| Capítul | o 1: (       | Generalidades del proyecto de grado        | 16   |

| 1.1.    | Inti         | roducción                                  | 16   |

| 1.2.    | An           | tecedentes                                 | 17   |

| 1.3.    | De           | finición del problema                      | 18   |

| 1.4.    | Ob           | jetivos                                    | 18   |

| 1.5.    | Hip          | oótesis                                    | 18   |

| 1.6.    | Me           | etodología de investigación                | 18   |

|         |              |                                            |      |

| Capítul | o 2:         | Fundamentación Teórica                     | 20   |

| 2.1.    | Inti         | roducción                                  | 20   |

| 2.2.    | De           | scripción básica de fisiología del corazón | 21   |

| 2.2     | 2.1.         | Anatomía del corazón                       | 21   |

| 2.2     | 2.2.         | Funcionamiento del corazón                 | 23   |

| 2.3.    | Se           | ñales electrocardiográficas                | 25   |

| 2.4.    | Me           | edición de señales ECG                     | 26   |

| 2.4     | <b>1</b> .1. | Derivación Einthoven                       | 26   |

| 2.4     | 1.2.         | Derivaciones aumentadas                    | 28   |

| 2.4     | 1.3.         | Derivaciones precordiales.                 | 29   |

| 2.5.    | Inte         | erpretación del ECG                        | 30   |

| 2.6.    | Tip          | oos de ondas en señales ECG                | 31   |

| 2.6     | §.1.         | Onda P                                     | 31   |

| 2.6     | 6.2.         | Onda compleja QRS                          | 31   |

| 2.6     | 6.3.         | Onda T                                     | 32   |

| 2.6     | 6.4.         | Onda U.                                    | 32   |

| 2   | 2.7.    | Inte | rvalos y segmentos de señales ECGs                      | 32 |

|-----|---------|------|---------------------------------------------------------|----|

|     | 2.8.    | Tec  | nología FPGA                                            | 33 |

|     | 2.8.    | 1.   | Flujo de diseño en FPGAs                                | 35 |

|     | 2.8.    | 2.   | Propiedades para implementaciones eficientes de FPGAs   | 36 |

|     | 2.9.    | Cor  | nfiguración del dispositivo FPGA                        | 37 |

|     | 2.9.    | 1.   | Entrada de diseño esquemático                           | 38 |

|     | 2.9.    | 2.   | Lenguajes de descripción de hardware                    | 38 |

|     | 2.9.    | 3.   | Lenguajes de alto nivel                                 | 39 |

| ;   | 2.10.   | Arq  | uitecturas FPGA                                         | 39 |

|     | 2.10    | 0.1. | FPGAs basados en memorias SRAM                          | 39 |

|     | 2.10    | 0.2. | FPGAs basados en antifuse                               | 40 |

|     |         |      |                                                         |    |

| Ca  | pítulo  | 3: C | esarrollo y Evaluación                                  | 42 |

| ;   | 3.1.    | Exp  | licación del trabajo de titulación                      | 42 |

| ;   | 3.2.    | Señ  | al ECG con filtrado digital FIR pasa bajo usando MatLab | 42 |

| ;   | 3.3.    | Dise | eño de la unidad de datos                               | 44 |

| ;   | 3.4.    | Dise | eño de la unidad de control                             | 46 |

| ,   | 3.5.    | Dise | eño de interfaz                                         | 48 |

| ,   | 3.6.    | Sist | ema en chip programable (SOPC)                          | 49 |

| ;   | 3.7.    | Dise | eño del Firmware                                        | 51 |

| ,   | 3.8.    | Res  | sultados obtenidos                                      | 52 |

|     | 3.8.    | 1.   | Datos de entrada                                        | 52 |

|     | 3.8.    | 2.   | Comparación de señales ECG                              | 55 |

|     | 3.8.    | 3.   | Limitaciones de hardware                                | 56 |

| _   | _       |      |                                                         |    |

|     |         |      | S                                                       |    |

|     |         |      | ciones                                                  |    |

| Kıl | olioara | atia |                                                         | 60 |

## **ÍNDICE DE FIGURAS**

| Capítulo 2:                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------|

| Figura 2. 1: Estructura general del corazón humano2                                                             |

| Figura 2. 2: Flujo sanguíneo del corazón humano                                                                 |

| Figura 2. 3: Descripción gráfica de conducción eléctrica del corazón humano                                     |

| 25                                                                                                              |

| Figura 2. 4: Triángulo de derivación Einthoven27                                                                |

| Figura 2. 5: Configuración de las derivaciones del plano frontal28                                              |

| Figura 2. 6: Configuración estándar de seis derivaciones precordiales30                                         |

| Figura 2. 7: Formas de ondas de una señal ECG típica3                                                           |

| Figura 2. 8: Formas de ondas de intervalos y segmentos de una señal ECG                                         |

| 33                                                                                                              |

| Figura 2. 9: Arquitectura básica del dispositivo electrónico FPGA34                                             |

| Figura 2. 10: Estructura del flujo de diseño en FPGAs35                                                         |

| Figura 2. 11: Propiedades para implementaciones eficientes36                                                    |

| Figura 2. 12: Esquemático típico para FPGAs basados en memorias SRAM                                            |

| Figure 2. 42. For war of time do médulo a lémico de Avadorator producido po                                     |

| Figura 2. 13: Esquemático de módulos lógicos de Axcelerator producido po                                        |

| Actel4                                                                                                          |

| Capítulo 3:                                                                                                     |

| Figura 3. 1: Tarjeta de entrenamiento de sistemas digitales Altera DE242                                        |

| Figura 3. 2: Señal ECG con ruido trazado en el dominio del tiempo y la                                          |

| frecuencia43                                                                                                    |

| Figura 3. 3: Señal de ECG filtrada usando MATLAB43                                                              |

| Figura 3. 4: Diagrama de bloques funcionales para la arquitectura del filtro FIR                                |

| Figura 3. 5: El diagrama de bloques de la unidad de datos para el filtro FIF                                    |

| pasa bajo sintetizado en Quartus II4                                                                            |

| Figura 3. 6: Gráfico de ASM para el diseño del filtro FIR pasa bajo47                                           |

|                                                                                                                 |

| Figura 3. 7: Diagrama de bloques de la conexión entre el filtro FIR pasa bajo con la interconexión del sistema. |

| con la inferconexión del sistema 49                                                                             |

| Figura 3. 8: Ventana principal de Altera SOPC Builder                     | .50 |

|---------------------------------------------------------------------------|-----|

| Figura 3. 9: Descarga de programación en Quartus II para el filtro FIR pa | ısa |

| pajo en FPGA DE2 de Altera                                                | .51 |

| Figura 3. 10: Muestra 1 de la señal bruta ECG                             | .53 |

| Figura 3. 11: Señal ECG filtrada utilizando la placa FPGA DE2 de Altera   | .53 |

| Figura 3. 12: Señal ECG filtrada usando MATLAB                            | .54 |

| Figura 3. 13: Muestra 2 de la señal ECG                                   | .54 |

| Figura 3. 14: Señal de ECG filtrada utilizando la placa Altera FPGA DE2   | .55 |

| Figura 3. 15: Señal ECG filtrada usando MATLAB                            | .55 |

## ÍNDICE DE TABLAS

| Capítulo 3:                                                          |

|----------------------------------------------------------------------|

| Tabla 3. 1: Señales vectoriales de control activadas y desactivadas4 |

#### Resumen

El presente documento del trabajo de titulación consiste en la implementación de un filtro digital FIR durante el procesamiento de señales ECG. La búsqueda de información relacionada al trabajo propuesto en repositorios y revistas fue de gran utilidad para cumplir con los objetivos planteados. En la primera parte se describen las generalidades del trabajo y en la segunda parte los elementos necesarios como la fisiología del corazón, la medición e interpretación de las señales ECGs, así como los tipos de ondas, intervalos y segmentos de una señal ECG. También se describe básicamente la tecnología, configuración y arquitecturas del dispositivo de arreglos de compuertas programables en campo conocido como FPGA. Finalmente, la última parte se realiza el diseño del filtrado digital FIR para eliminación de ruido. Esta parte se utiliza la tarjeta de entrenamiento FPGA DE2 de Altera, en la que se trabaja eficientemente en la muestra de resultados. También, fue necesaria el uso de la herramienta FDA de Matlab para el filtro digital FIR.

**Palabras clave:** SEÑAL ECG, PROCESAMIENTO, RUIDO, FILTROS, FIR, FPGA.

#### Abstract

This research paper is about the implementation of the digital filter FIR during the ECG signal processing. Looking for information related to this research in archives and magazines was of utmost utility in order to comply with the objectives laid out. The first part provides general information about the research. The second part delivers the required elements, such as the physiology of the heart, measuring and interpretation of the ECG signals, as well as the types of waves, and intervals and segments of an ECG signal. This part also describes basically the technology, configurations and architectures of the field-programmable gate array, also known as FPGA. Finally, in the last part, the design of the digital filter FIR is carried out in order to eliminate noise. For this part the Altera DE2 Development and Education Board was used, with which the result samples have been gathered effectively. The use of FDATool of MATLAB was also required for the digital filter FIR.

Key words: ECG SIGNAL, PROCESSING, NOISE, FILTERS, FIR, FPGA.

#### Capítulo 1: Generalidades del proyecto de grado.

#### 1.1. Introducción.

Según Jagadiswara R. & Usharani, (2013) las señales biomédicas son producidas por las actividades fisiológicas en el organismo, tales como, organismos vivos, desde las secuencias de genes y proteínas hasta los ritmos neuronales y cardíacos, son capaces de producir señales. También manifiestan que la señales podrían ser observadas o monitoreadas para realizar algunos aspectos de un sistema fisiológico particular. En la asistencia médica, la señal cardiaca, conocida como ECG, que es la señal más común utilizada por los médicos para evaluar las anomalías cardíacas del ser humano.

Mientras que para Mbachu & Offor, (2013) la señal ECG es muy vital en el seguimiento clínico y el diagnóstico de las condiciones de salud del corazón humano. Las señales más significativas de la señal ECG son la interferencia de línea eléctrica y señales biomédicas como el electromiograma (EMG), la deriva de línea de base y el electroencefalograma (EEG). Para la correcta extracción de las características de la señal de ECG, estas señales significativas del ECG tienen que ser cancelado.

Una vez descrito brevemente la parte de señales biomédicas, en especial de las señales ECGs. Ahora corresponde brevemente describir la parte del filtrado, que es muy importante a la hora de procesar señales ECGs. Para Mamatha & Ramachandram, (2012) los filtros son un componente básico de todos los sistemas de procesamiento de señales y telecomunicaciones. También, sostienen que los filtros se emplean ampliamente en sistemas de procesamiento de señales y comunicaciones en aplicaciones tales como ecualización de canales, reducción de ruido, radar, procesamiento de audio, procesamiento de video, procesamiento de señales biomédicas y análisis de datos económicos y financieros.

#### 1.2. Antecedentes.

En nuestro país el estudio del procesamiento de señales biomédicas es muy reducido, muy pocas Instituciones de Educación Superior (IES) tienen líneas de investigación en la que trabajen con adquisición, pre-procesamiento y procesamiento de señales biomédicas, en especial las señales ECGs. En esta línea de investigación pueden desarrollarse múltiples trabajos investigativos que tributen a la publicación de artículos científicos en revistas o congresos de ingeniería en telecomunicaciones y electrónica. Durante la fase de búsqueda de información se encontraron con importantes trabajos publicados en revistas internacionales.

Los autores Jagadiswara R. & Usharani, (2013) muestran su investigación de "Mejoramiento de las señales ECG mediante el uso de filtros digitales FIR", donde muestran la eliminación de la interferencia de baja frecuencia, es decir, el desplazamiento de la línea base y el ruido de alta frecuencia, es decir, la electromiografía en la señal ECG y para lo cual los filtros digitales se implementan para suprimirlo. Los filtros digitales realizados son FIR con varios métodos de ventana como Rectangular, Hann, Blackman, Hamming y Kaiser.

Otro trabajo "Reducción del ruido de la red eléctrica en señales ECG usando filtro digital FIR implementado con la ventana de Hamming" desarrollado por los autores Mbachu & Offor, (2013). Este trabajo investigativo, se muestra el diseño de filtros digitales para suprimir estos ruidos, ya que es importante en el procesamiento de señales ECG. En este trabajo se diseña e implementa con la ventana de Hamming un filtro digital FIR para reducir el ruido de línea eléctrica de 50 Hz en la señal de ECG. Utilizan la herramienta (Tool) FDA de MatLab para generar la señal ECG y el ruido, y también la observación de los resultados.

Estos dos trabajos han sido de gran utilidad para el desarrollo del presente trabajo de maestría.

#### 1.3. Definición del problema

Actualmente no se tienen muchos trabajos de maestría en la que se desarrollen proyectos relacionados con el procesamiento ni filtrado de señales ECG. Para lo cual, surge la necesidad de la implementación del procesamiento de señales ECG mediante filtrado digital FIR utilizando el dispositivo programable FPGA DE2 de Altera.

#### 1.4. Objetivos

#### 1.4.1. Objetivo General.

Realizar la implementación de procesamiento de señales ECG mediante filtrado digital FIR utilizando el dispositivo programable FPGA DE2 de Altera.

#### 1.4.2. Objetivos específicos.

- Describir la fundamentación teórica de las señales electrocardiográficas y del dispositivo FPGA.

- ✓ Realizar el diseño y programación del procesamiento de señales ECG mediante el filtrado digital finito de respuesta impulsional utilizando la placa FPGA DE2.

- ✓ Evaluar los resultados obtenidos en la adquisición y tratamiento del filtro de la señal ECG.

#### 1.5. Hipótesis

La implementación de procesamiento de señales ECG mediante filtrado digital FIR utilizando el dispositivo programable FPGA permitirá la eliminación de ruido que se genera al momento de adquirir señales ECGs. Como hipótesis nula sería: El filtro digital FIR implementado reducirá el ruido presentado al adquirir la señal ECG.

#### 1.6. Metodología de investigación.

La metodología utilizada en el presente trabajo tiene un enfoque cuantitativo, cuyo diseño de investigación es descriptivo, exploratorio y explicativo. Descriptivo, ya que se fundamenta los elementos teóricos que dan

soporte al trabajo; es exploratorio, porque se revisan trabajos relacionados al filtrado digital de las señales ECGs para eliminación de ruido causado en la adquisición del ECG; y es explicativo, porque se detalla cada uno de los elementos que intervienen en el desarrollo del procesamiento de señales ECG mediante filtrado digital FIR utilizando el dispositivo programable FPGA

#### Capítulo 2: Fundamentación Teórica

#### 2.1. Introducción

Antes de intentar cualquier procesamiento de señales de ECG, es importante comprender primero la base fisiológica del ECG, revisar los convenios de medición del ECG estándar y revisar cómo un clínico usa los ECG para el cuidado del paciente. Entender la base de un ECG normal requiere la apreciación de cuatro aspectos:

- Fisiología de las estructuras específicas del corazón,

- Electrofisiología del corazón y el origen del ECG,

- Medición y registro del ECG,

- Interpretación del ECG en el contexto clínico.

En torno a estos cuatro aspectos, se describirán en las dos primeras secciones cómo la onda de corriente eléctrica se propaga a través del músculo cardíaco, la fisiología de las estructuras específicas del corazón a través del cual viaja la onda eléctrica, cómo conduce a una señal medible en la superficie del cuerpo, produciendo un ECG normal, y la última cómo un cardiólogo interpreta el ECG.

Es importante señalar que existen muchos trabajos investigativos en los últimos 10 años, entre los cuales se dispone de muchos detalles sobre la actividad electrofisiológica del corazón y está sección es sólo un resumen abreviado. Como se menciona en la introducción general, la detección / estimación y delineación de cada componente de onda de la señal de ECG es un paso crucial para la interpretación de ECG. También, se describirá al final del presente capítulo los métodos de procesamiento de señales ECG opuestos al iniciar esta sección, con el énfasis en la detección de la onda y delineación.

#### 2.2. Descripción básica de fisiología del corazón.

Según López Farré & Macaya Miguel, (2009) el corazón es un músculo que es rítmicamente impulsado a contraerse y por lo tanto impulsar la circulación de la sangre en todo el cuerpo. Antes de cada latido cardíaco normal, o sístole, una onda de corriente eléctrica pasa por todo el corazón, lo que desencadena la contracción miocárdica. El patrón de propagación eléctrica no es aleatorio, sino que se extiende sobre la estructura del corazón en un patrón coordinado que conduce a una sístole eficaz y coordinada. Esto resulta en un cambio mensurable en la diferencia de potencial en la superficie corporal del sujeto. La señal amplificada (y filtrada) resultante se conoce como ECG. Para entender el origen del ECG, se debe comenzar con la estructura del corazón y su funcionamiento.

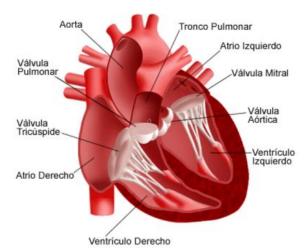

#### 2.2.1. Anatomía del corazón

El corazón consta de cuatro cámaras, dos cámaras auriculares (atrio) en el corazón superior y dos cámaras ventriculares (ventrículos) en la parte inferior, tal como se ilustra en la figura 2.1. El atrio son las cámaras de recepción y los ventrículos son las cámaras de descarga. El corazón está constituido principalmente por un tipo especializado de músculo estriado, con propiedades que funcionan de manera algo diferente que el músculo esquelético.

Figura 2. 1: Estructura general del corazón humano. Fuente: (Blázquez D., 2017)

Las células del corazón están conectadas por uniones de hueco que permiten que los iones fluyan de una célula a otra, permitiendo una rápida propagación de la despolarización. Una colección de células del corazón conectadas de esta manera constituye un sincitio. El corazón se compone de dos sincitios: un sincitio auricular y un sincitio ventricular.

El músculo, que es como una pared alrededor del corazón, se llama el miocardio. Los dos ventrículos están separados por el tabique ventricular, que es grueso muscular hacia el fondo, y grueso fibroso en la parte superior. Bajo el miocardio está el endocardio, que recubre las cámaras del corazón, y que está compuesto principalmente de células epiteliales. El pericardio es un saco de doble pared que contiene el corazón y las raíces de los grandes vasos. La pared externa del pericardio se compone de tejido conectivo denso. La parte de la pared interna del pericardio que está en contacto con el corazón (pero no en contacto con los grandes vasos) es el epicardio. El epicardio contiene los vasos sanguíneos que suministran sangre al músculo cardíaco (las arterias coronarias) así como a las fibras nerviosas.

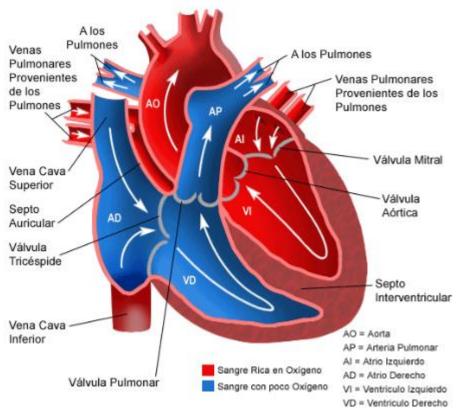

De acuerdo con Aequum, (2016) las venas del cuerpo humano terminan en dos grandes vasos vaciados en el atrio derecho. Estas venas se denominan: vena cava superior (parte superior del corazón) y vena cava inferior (parte inferior del corazón). En las figuras 2.1 y 2.2 se puede observar como la sangre sale del corazón mediante la arteria pulmonar (que lleva la sangre no oxigenada a los pulmones desde el ventrículo derecho) y mediante la aorta (que distribuye sangre oxigenada al cuerpo desde el VI). La sangre oxigenada de los pulmones entra en la aurícula izquierda de la vena pulmonar. La arteria pulmonar es la única arteria que lleva sangre no oxigenada y la vena pulmonar es la única que lleva sangre oxigenada.

Figura 2. 2: Flujo sanguíneo del corazón humano. Fuente: (Blázquez D., 2017)

#### 2.2.2. Funcionamiento del corazón.

El corazón bombea sangre en un proceso de dos pasos. Las aurículas inyectan sangre en los ventrículos y luego los ventrículos extraen sangre del corazón. Las cámaras del corazón se llenan de sangre durante una fase de relajación (diástole) y expulsan sangre durante una fase de contracción (sístole). La sístole auricular precede a la sístole ventricular. La sístole y la diástole del ventrículo izquierdo corresponden a las fases sistólica (alta presión) y diastólica (presión más baja) de la presión sanguínea en el cuerpo (Aequum, 2016).

En la figura 2.2 se puede apreciar que la aurícula derecha bombea sangre desde el cuerpo hacia el ventrículo derecho. El ventrículo derecho bombea sangre a los pulmones. La aurícula izquierda bombea la sangre de los pulmones hacia el ventrículo izquierdo. El ventrículo izquierdo bombea

sangre al cuerpo a través de la aorta. Este ciclo de sangre por el corazón se llama ciclo cardíaco.

El ventrículo izquierdo tiene la musculatura más poderosa en la medida en que debe bombear sangre en todo el cuerpo. Para el ventrículo izquierdo el ciclo cardiaco se puede describir en cuatro fases:

#### 1. Período de llenado.

El volumen aumenta entre 50 ml y 120 ml de sangre aproximadamente, después de lo cual la válvula mitral se cierra. El 70% del llenado ventricular ocurre pasivamente a medida que la sangre fluye hacia las aurículas a través de los ventrículos mientras la válvula tricúspide está abierta. La contracción auricular empuja el 30% final de la sangre hacia el ventrículo, después de lo cual la válvula tricúspide se cierra.

#### 2. Período de contracción isovolumétrica.

Todas las válvulas están cerradas a medida que la presión aumenta de 5 mmHg a 80 mmHg mientras que el volumen de sangre permanece inalterado.

#### 3. Período de expulsión.

La válvula aórtica se abre y la sangre es expulsada en el cuerpo. El 70% del vaciado de la sangre ocurre en el primer tercio del período de eyección a medida que la presión aumenta a 120 mmHg. La presión cae a 100 mmHg durante los últimos dos tercios del período de eyección.

#### 4. Período de relajación isovolumétrica.

La presión cae a cero después de que la válvula aórtica se haya cerrado.

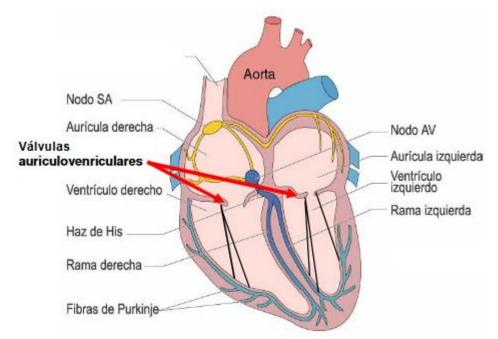

El sistema de conducción eléctrica del corazón se muestra en la figura 2.3. La despolarización y contracción del músculo cardíaco está precedida por la despolarización de los haces de nervios cardíacos. La despolarización del

corazón se inicia en el nodo sino auricular (nodo SA) situado en la aurícula derecha. La despolarización se transmite a través del nódulo auricular ventricular (nódulo A-V), el haz de His y luego a través de los ventrículos por las fibras de Purkinje. El ciclo cardiaco se inicia en el nódulo SA de la aurícula, llamada despolarización auricular, lo que provoca la contracción del sincitio auricular. A diferencia de las células cardíacas que tienen función mecánica (mecánica), las células cardíacas que tienen una función de conducción eléctrica no sólo conducen impulsos eléctricos, sino que generan impulsos espontáneamente.

Figura 2. 3: Descripción gráfica de conducción eléctrica del corazón humano. Fuente: (Ramón S., 2015)

#### 2.3. Señales electrocardiográficas.

La conducción eléctrica del corazón puede proyectarse sobre diferentes líneas de orientación bien definida sobre la superficie de la piel. La derivación (lead) electrocardiografía es una línea que conecta dos puntos de observación de la actividad eléctrica del corazón a partir de la cual se mide una diferencia de potencial eléctrico. Cada derivación revela la magnitud de la conducción eléctrica en la dirección de esa derivación en cada instante de tiempo. En esta sección se describe cómo la conducción eléctrica de un ciclo cardiaco resulta

en el patrón de un electrocardiograma (ECG) escalar normal y se presenta la interpretación clínica de la señal ECG.

#### 2.4. Medición de señales ECG.

Las máquinas de monitoreo de señales ECG generalmente pueden registrar varias diferencias de potencial al mismo tiempo según la ubicación y el número de electrodos ubicados en el cuerpo. Los electrodos adicionales proporcionan un monitoreo más sensible de la despolarización. Cada medición del potencial corresponde a una derivación del ECG. Obsérvese que el término "derivación" puede ser confuso en la medida en que las derivaciones estándar de los miembros son bipolares (medir la diferencia de potencial entre dos electrodos) mientras que las otras son unipolares (electrodo único).

El ECG de 12 derivaciones, contiene seis derivaciones delanteras y seis precordiales, la misma ha sido estandarizado por una convención internacional. Los diferentes puntos de vista ofrecidos por el ECG de 12 derivaciones permiten una representación tridimensional de la actividad eléctrica del corazón. El sistema estándar de ECG de 12 derivaciones se compone de la siguiente manera:

- ❖ 3 derivaciones Einthoven bipolares de los miembros: D1, D2 y D3,

- 3 derivaciones unipolares de extremidades aumentadas: aVR, aVL y aVF.

- ❖ 6 derivaciones unipolares precordiales: V1, V2, V3, V4, V5 y V6.

A continuación, se presentan las posiciones de los electrodos correspondientes a cada tipo de derivación:

#### 2.4.1. Derivación Einthoven.

Al inicio del siglo XX, Willem Einthoven descubrió que la despolarización del corazón puede ser monitorizada con tres electrodos unidos al cuerpo: uno

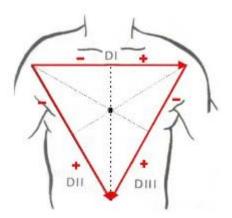

en cada brazo y uno en la pierna izquierda. La despolarización se extiende desde la aurícula derecha (correspondiente al electrodo del brazo derecho) hasta el ventrículo izquierdo (correspondiente al electrodo de la pierna izquierda). El electrodo del brazo izquierdo es neutro. Basado en este principio, inventó un sistema de tres derivaciones de la grabación del ECG (derivaciones estándar del miembro) a la que se ha añadido tres salidas de extremidad aumentada y seis derivaciones de pecho en el moderno ECG de 12 derivaciones. Las derivaciones estándar (véase la figura 2.4) de las extremidades son:

- Derivación I (DI): diferencia de potencial entre el brazo izquierdo (electrodo positivo) y el brazo derecho (electrodo negativo),

- Derivación II (DII): diferencia de potencial entre la pierna izquierda (electrodo positivo) y el brazo derecho (electrodo negativo),

- ❖ Derivación III (DIII): diferencia de potencial entre la pierna izquierda (electrodo positivo) y el brazo izquierdo (electrodo negativo).

Figura 2. 4: Triángulo de derivación Einthoven. Fuente: (Cardona, Mayoral, & Muñoz, 2010)

Hay que tener en cuenta que el brazo izquierdo es positivo en relación con el brazo derecho y negativo en relación con la pierna izquierda. Hay redundancia en el uso de estas tres derivaciones bipolares, por ejemplo, en la medida en que la tensión registrada en la derivación II es la suma de las tensiones de las otras dos derivaciones (I + III = II). Se registra una forma de

onda positiva (tensión positiva) cuando la despolarización fluye de un electrodo negativo a un electrodo positivo. Por esta razón, la derivación II típicamente da patrones de ECGs canónicos porque el flujo de despolarización del electrodo negativo (brazo derecho) al electrodo positivo (pierna izquierda) coincide con la alineación típica del corazón en el pecho: inclinado hacia abajo hacia el lado izquierdo del cuerpo.

#### 2.4.2. Derivaciones aumentadas.

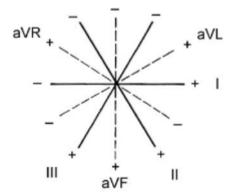

Como se observó en la figura 2.4 (las derivaciones I, II y III) estas derivaciones dan una visión del corazón llamada triángulo de Einthoven, que divide un círculo de 360° centrado en el corazón en tres ejes de despolarización separados por 120°. La adición de las tres derivaciones aumentadas de la extremidad de Goldberger divide el corazón en seis ejes de despolarización separados por 60°, tal como se muestra en la figura 2.5.

Las derivaciones aumentadas de la extremidad son:

- aVR: diferencia de potencial entre el brazo derecho (electrodo positivo)

y el centro del corazón,

- aVL: diferencia de potencial entre el brazo izquierdo (electrodo positivo)

y el centro del corazón,

- aVF: diferencia de potencial entre la pierna izquierda (electrodo positivo) y el centro del corazón.

Figura 2. 5: Configuración de las derivaciones del plano frontal. Fuente: (Dupre, Vieau, & laizzo, 2009)

Par fines prácticos, "a" se denota como aumentado, mientras que "V" denota Voltage, y la letra final designa el brazo derecho o izquierdo, o la pierna izquierda. La inclusión tanto de direcciones positivas como negativas de despolarización tanto de las derivaciones estándar como aumentadas da un círculo de 360° dividido en doce secciones de 30° que se denomina sistema de referencia hexaxial.

La derivación I (que apunta hacia el brazo izquierdo) se toma como la referencia para la orientación de derivación de 0°, aumentando los valores positivos en el sentido de las agujas del reloj a 180° y aumentando los valores negativos en el sentido antihorario, tal que -180° es la misma orientación que +180°. Aunque la derivación II, con una orientación de aproximadamente 60°, es la orientación más típica de un eje que apunta desde la aurícula a los ventrículos, no es anormal que la orientación del corazón esté en el intervalo de -30° a +110°, lo que puede hacer que las derivaciones aVL, aVF o III en lugar de la derivación II, el indicador primario de la despolarización cardiaca normal.

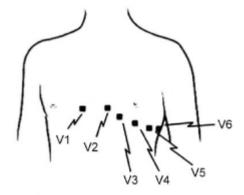

#### 2.4.3. Derivaciones precordiales.

El sistema hexaxial de referencia de 360° define lo que se denomina el plano frontal de la monitorización de ECG - una vista del corazón desde el frente para proporcionar una vista a través del plano horizontal (viendo el corazón como si el cuerpo fuera cortado horizontalmente a través del centro del pecho) se colocan seis cables precordiales "unipolares" adicionales (designados V1 a V6) en las posiciones de la costilla izquierda formando un cuarto de círculo alrededor del corazón (véase la figura 2.6). El ECG representa la diferencia entre cada uno de estos electrodos (V1-V6) y el terminal central.

Figura 2. 6: Configuración estándar de seis derivaciones precordiales. Fuente: (Dupre et al., 2009)

#### 2.5. Interpretación del ECG.

Para el caso de las 12 derivaciones, las seis primeras derivan de los mismos tres puntos de medición. Por lo tanto, cualquiera de estas dos derivaciones incluye exactamente la misma información que las otras cuatro. Más del 90% de la actividad eléctrica del corazón puede explicarse con un modelo de fuente dipolar. Para evaluar este dipolo, basta con medir sus tres componentes independientes. En principio, dos de las derivaciones de las extremidades (I, II, III) podrían reflejar los componentes del plano frontal, mientras que una derivación precordial podría ser elegido para el componente anterior-posterior.

La combinación debe ser suficiente para describir completamente el vector del corazón eléctrico. La derivación V2 sería una muy buena elección de derivación precordial ya que está dirigido más cerca del eje x, es más o menos ortogonal al plano frontal. La principal razón para registrar las 12 derivaciones es que mejora el reconocimiento de patrones. Esta combinación de derivaciones da al clínico la oportunidad de comparar las proyecciones de los vectores resultantes en dos planos ortogonales y en diferentes ángulos. La información útil que se puede extraer de la señal de ECG, así como el procedimiento clínico de interpretación de ECG, tales como las ondas: P, QRS, T y U.

#### 2.6. Tipos de ondas en señales ECG.

De acuerdo a lo descrito en la sección 2.2.2, cada ciclo cardíaco (solamente personas sanas) consiste en la misma fase de despolarización / repolarización de las aurículas a los ventrículos. La proyección de superficie del potencial de acción eléctrico del corazón es, por lo tanto, una señal pseudo-periódica en el sentido de que el ciclo cardiaco se repite de acuerdo con la frecuencia cardiaca.

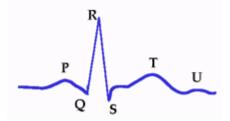

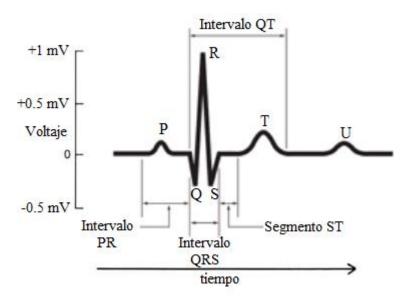

Un electrocardiograma es una medida de la actividad eléctrica del músculo cardíaco que puede obtenerse de la superficie de la piel y desde diferentes ángulos (Jaber & Cankaya, 2015). En cada ciclo, las ubicaciones de diferentes ondas en el ECG se marcan arbitrariamente con las letras P, Q, R, S, T y U, tal como se ilustra en la figura 2.7.

Figura 2. 7: Formas de ondas de una señal ECG típica. Fuente: (My EKG, 2015)

#### 2.6.1. Onda P.

Este tipo de onda está relacionada con la despolarización auricular. El vector eléctrico principal se dirige desde el nodo sinoauricular hacia el nodo A-V, y se extiende desde la aurícula derecha hasta la aurícula izquierda. La onda P generalmente tiene pequeña amplitud de onda, con forma de onda redondeada, a veces bifásica.

#### 2.6.2. Onda compleja QRS.

La onda QRS refleja la rápida despolarización de los ventrículos derecho e izquierdo. Tienen una gran masa muscular en comparación con las aurículas y por lo que el complejo QRS por lo general tiene una amplitud mucho mayor

que las ondas P y T. Por definición, la onda Q es la primera onda negativa, la onda R es la primera onda positiva del complejo y la onda S es la primera onda negativa después de la onda R.

#### 2.6.3. Onda T.

La onda T representa la repolarización de los ventrículos. Esta onda sigue al complejo QRS después de regresar a la línea isoeléctrica. El intervalo desde el comienzo de la onda compleja QRS hasta el ápice de la onda T que se conoce como el período refractario absoluto.

#### 2.6.4. Onda U.

La onda U hipotéticamente es causada por la repolarización del tabique interventricular. Normalmente tiene una amplitud baja, y aún más es a menudo completamente ausente. Siempre sigue la onda T y también sigue la misma dirección en amplitud.

#### 2.7. Intervalos y segmentos de señales ECGs.

Los intervalos y segmentos de un ECG son parámetros importantes para evaluar la normalidad o anomalía del espacio entre dos eventos eléctricos, por lo que son generalmente clínicamente relevantes. En la figura 2.8 se muestran las características clínicas normales del electrocardiograma, que incluyen las amplitudes de onda y los intervalos entre ondas (intervalos de ECG). Hay que tener en cuenta que la sincronización entre latidos (intervalo RR) no está marcada.

Los valores de las características clínicas indicadas en la figura 2.8 son típicos, aunque pueden variar según el género, la edad, la actividad y la salud. La interpretación clínica de los segmentos e intervalos de ECG se puede resumir como: intervalo PR (o PQ), intervalo QT, segmento ST e intervalo QRS.

Figura 2. 8: Formas de ondas de intervalos y segmentos de una señal ECG. Fuente: (Larroza S., Zena G., & Frutos O., 2008)

#### 2.8. Tecnología FPGA.

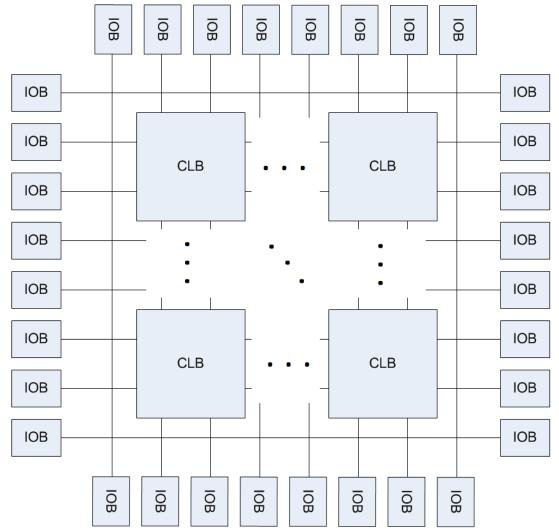

Un FPGA es un dispositivo semiconductor reprogramable que está diseñado para ser reconfigurable. Es decir, que puede ser reprogramado las veces que sean necesarias, aún si el diseñador ha desarrollado alguna aplicación. La tecnología FPGA sigue ganando impulso desde su invención en 1984 por el fabricante Xilinx. Inicialmente fue muy utilizada para aplicaciones de sistemas digitales, y en la actualidad para el desarrollo de aplicaciones modernas de alto rendimiento.

El éxito de la tecnología FPGA es atribuible a las capacidades y ventajas tecnológicas, tales como la canalización también conocida como pipeline, el paralelismo, la reconfigurabilidad dinámica y el ciclo de desarrollo de prototipos rápidos. La arquitectura básica de una FPGA se muestra en la figura 2.9. La matriz de bloques lógicos configurables (CLBs) puede configurarse individualmente como un bloqueo de reinicio (SRL), memoria de acceso aleatorio (RAM) o tabla de búsqueda (LUT). Los bancos de entrada / salida (IOBs) proporcionan un puente de interfaz en el sistema interno.

Figura 2. 9: Arquitectura básica del dispositivo electrónico FPGA. Fuente: (Herrera L. & González R., 2015)

El software de diseño, como Quartus II de Altera interconecta señales entre CLBs e IOBs para crear un sistema personalizado en el dispositivo FPGA. El número de puertas lógicas en FPGAs ha estado aumentando desde los años 1980, de miles, a diez miles, a cientos de miles, y ahora millones. Actualmente es posible implementar algoritmos mayores y más complejos en FPGAs, tales como transformadas rápidas de Fourier y procesamiento de señales biomédicas.

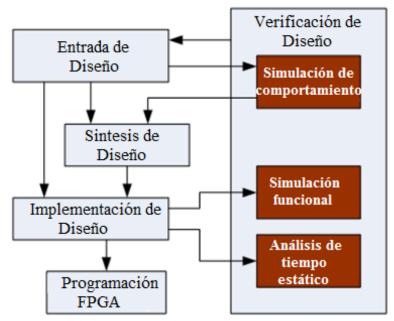

#### 2.8.1. Flujo de diseño en FPGAs.

En la figura 2.10 se muestra el proceso para el flujo de diseño en FPGAs estándar, el mismo comprende los siguientes pasos: entrada de diseño, síntesis de diseño, implementación de diseño y descarga a un dispositivo FPGA. Las técnicas de verificación de diseño se llevan a cabo a través de diferentes etapas del flujo de diseño. Estas técnicas incluyen la simulación de comportamiento, simulación funcional y análisis de tiempo estático.

Figura 2. 10: Estructura del flujo de diseño en FPGAs. Fuente: (Chu, 2008)

Para la parte de entrada y síntesis de diseño, se crea una descripción completa del comportamiento deseado del sistema que se va a desarrollar utilizando un editor de esquemas compatible con el proveedor, un lenguaje de descripción del hardware (HDL) o ambos. Esta entrada de diseño debe ser sintetizada para el dispositivo FPGA de destino. El proceso de síntesis traduce la información de comportamiento y las restricciones de usuario en una netlist estructural para el dispositivo FPGA especificado. La funcionalidad se verifica mediante la simulación antes de implementar el diseño. El entorno de simulación no se ejecuta en tiempo real, sino que los comportamientos de las señales internas en cada período de tiempo se calculan y se simulan.

Mientras que, para la implementación y descarga del diseño, este proceso se asigna el diseño lógico al dispositivo FPGA de destino. El diseño del circuito mapeado se coloca y enruta. Se genera un flujo de bits (bitstream) de configuración (un archivo binario con extensión BIT) para el dispositivo FPGA mediante la información colocada y enrutada. El archivo BIT generado puede ser descargado en un dispositivo FPGA o formateado en un archivo de memoria programable de sólo lectura (PROM) para almacenamiento en memoria no volátil.

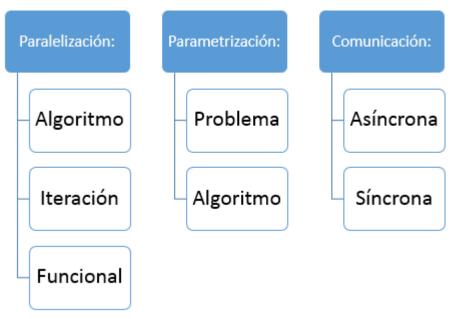

#### 2.8.2. Propiedades para implementaciones eficientes de FPGAs.

El diseño de una arquitectura de computación de hardware dedicada eficiente, como una FPGA, requiere la previsión de tres propiedades de implementación: paralelización, parametrización y comunicación. Estas propiedades de implementación se muestran en la figura 2.11.

Figura 2. 11: Propiedades para implementaciones eficientes. Fuente: (Chu, 2008)

a) Paralelización: la paralelización puede extenderse a un nivel de algoritmo de optimización, que incluye múltiples algoritmos de optimización que procesan de forma independiente o conjuntamente;

- un nivel de iteración, que maneja simultáneamente la población de soluciones; y funcional, ya que sincroniza la ejecución de las funciones y datos particionados.

- b) Parametrización: los recursos finitos en un dispositivo FPGA determinad, limitan los bits de variable permitidos para la configuración de parámetros tanto en el problema como en el algoritmo. En cuanto al diseño de algoritmos evolutivos (Evolutionary Algorithm, EA) basadas en FPGA para problemas de optimización, los parámetros dependen del problema que incluyen las variables de decisión y los límites de cada variable, mientras que los parámetros para las EAs incluyen el tamaño de la población y la resolución de la solución.

- c) Comunicación: el nivel de comunicación determina el caudal de canalización del sistema general. El intercambio de información y las operaciones entre módulos internos pueden ser una etapa a la vez o múltiples etapas que ocurren simultáneamente, ya sean asíncronas o sincrónicas respectivamente. La comunicación síncrona produce un rendimiento más alto, pero a expensas de la complejidad del diseño.

El diseño de algoritmos para una implementación de FPGA comienza con la consideración deliberada de tales propiedades de implementación. La justificación de la utilización de diferentes conjuntos de propiedades depende del requisito general del sistema para la aplicación dada, como la complejidad del algoritmo, las restricciones de problemas y los recursos disponibles.

# 2.9. Configuración del dispositivo FPGA.

Definir manualmente las conexiones de enrutamiento en un dispositivo programable puede haber sido factible con las primeras matrices lógicas programables (*Programmable Array Logics, PALs*), pero es casi imposible teniendo en cuenta la densidad de las FPGAs modernas. La configuración de

estos dispositivos programables puede lograrse de varias maneras, como la introducción de diseño esquemático, el uso de lenguajes de descripción de hardware (Hardware Description Language, HDLs) y el uso de compiladores de lenguaje de alto nivel. Estos métodos se enumeran en niveles crecientes de abstracción, siendo la entrada de diseño esquemática el nivel más bajo.

# 2.9.1. Entrada de diseño esquemático.

Las prácticas de diseño esquemático implican la selección de puertas lógicas estándar de una biblioteca para crear una descripción gráfica del circuito a realizar y el cableado manual entre sí. La biblioteca de diseño esquemático incluye típicamente puertas lógicas booleanas estándar, multiplexores, memorias intermedias de E/S y macros para funciones específicas del dispositivo, como divisores de reloj. Los componentes personalizados pueden construirse a partir de los bloques más pequeños para crear macros de usuario para su uso en diseños grandes.

# 2.9.2. Lenguajes de descripción de hardware.

Los lenguajes de descripción de hardware más populares son Verilog y VHDL. Ambos son descripciones basadas en texto del comportamiento del circuito digital, y su sintaxis contiene anotaciones explícitas para expresar tiempo y concurrencia. Gateway Design Automation Inc. comenzó el lenguaje Verilog alrededor de 1984 como un lenguaje de modelado de hardware propietario. El lenguaje se hizo público en 1990 y desde entonces ha sido muy popular en la industria de semiconductores para diseños ASIC y FPGA.

VHDL es un lenguaje de descripción de hardware que surgió del programa VHSIC patrocinado por el Departamento de Defensa de los Estados Unidos y fue lanzado por primera vez en 1985. El acrónimo VHDL, significa VHSIC Hardware Description Language, con el acrónimo VHSIC de Very High-Speed Integrated Circuit (circuito integrado de muy alta velocidad).

# 2.9.3. Lenguajes de alto nivel.

Existe un creciente interés en el uso de lenguajes de programación de alto nivel para el diseño FPGA. Algunos generan un código HDL a partir de un lenguaje similar a C. Por ejemplo, Confluence, que se basa en Python, también toma este enfoque. El lenguaje personalizado se compila para generar una descripción de circuito VHDL o Verilog. También cuenta con una herramienta que produce similarmente una descripción de circuito de nivel de transferencia de registro (RTL) de un archivo m de MatLab.

Un acercamiento alternativo es generar el netlist del dispositivo directamente forma la descripción de alto nivel. Esto es lo que hace el lenguaje Quartus II de Altera y otras plataformas como Xilinx. Un defecto de los lenguajes de diseño de alto nivel es su incapacidad de instanciar funciones específicas del proveedor, tales como bloques RAM y bloques DSP.

## 2.10. Arquitecturas FPGA.

Esta sección proporciona una descripción detallada de dos arquitecturas FPGA propuestas en estudios previos de FPGA, incluyendo una arquitectura FPGA convencional y otra orientada a datos. Cada FPGA se describe en términos de su arquitectura:

# 2.10.1. FPGAs basados en memorias SRAM.

El FPGA basado en memorias SRAM almacena los datos de configuración de las celdas lógicas en la memoria estática (organizada como un conjunto de latches) tal como se muestra en la figura 2.12. Dado que una SRAM es volátil y no puede mantener los datos sin una fuente de alimentación, tales FPGAs, deben ser programados (configurados) al arrancar. Hay dos modos básicos de programación:

a) Modo maestro, cuando la FPGA lee datos de configuración de una fuente externa, como un chip de memoria flash externo.

b) Modo esclavo, cuando una FPGA está configurada por un dispositivo maestro externo, como un procesador. Esto se puede hacer generalmente a través de una interfaz de configuración dedicada o a través de una interfaz de frontera de exploración (JTAG).

Todas las FPGAs basadas en memorias SRAM incluyen la mayoría de los chips de las familias Xilinx (Virtex y Spartan) y Altera (Stratix y Cyclone).

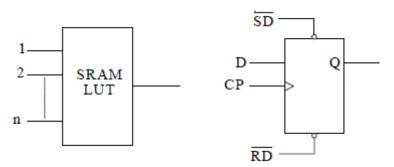

Figura 2. 12: Esquemático típico para FPGAs basados en memorias SRAM. Fuente: (Karris, 2005)

#### 2.10.2. FPGAs basados en antifuse.

Los FPGAs basados en antifuse son diferentes de los anteriores, ya que sólo se pueden programar una vez. El antifuse es un dispositivo que no conduce la corriente inicialmente, pero puede ser "quemado" para conducir la corriente (el comportamiento del antifuse es así opuesto al del fusible, de ahí el nombre). El FPGA basado en antifuse no se puede reprogramar ya que no hay manera de devolver un antifuse quemado al estado inicial. Las familias de dispositivos basados en antifuse incluyen Axcelerator producido por Actel.

Axcelerator de Actel ofrece dos tipos de módulos lógicos: la celda combinatoria (celda C) y la celda de registro (celda R) tal como se muestra en la figura 2.13. La celda C puede implementar más de 4.000 funciones combinacionales de hasta cinco entradas, mientras que la celda R contiene un Flip-Flop con señales asíncronas, presintonías asíncronas y activas. Los registros de celdas R tienen una polaridad de reloj programable seleccionable en base de registro por registro.

Figura 2. 13: Esquemático de módulos lógicos de Axcelerator producido por Actel. Fuente: (Karris, 2005)

# Capítulo 3: Desarrollo y Evaluación.

En esta sección se realiza el desarrollo y evaluación del proyecto de titulación denominado "Implementación de procesamiento de señales ECG mediante filtrado digital FIR utilizando el dispositivo programable FPGA".

# 3.1. Explicación del trabajo de titulación.

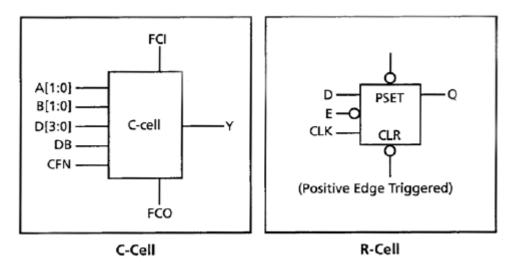

El objetivo final de este proyecto es conseguir que el filtro FIR pasa bajo funcione con el procesador NIOS II en la placa de entrenamiento Altera DE2 (véase la figura 3.1). Para lograr este objetivo, el diseño del filtro FIR pasa bajo se divide en dos partes principales. En primer lugar, el filtro se diseña inicialmente utilizando MatLab. Después, las señales electrocardiográficas (ECG) se filtran usando la misma plataforma en que fue diseñado para probar la funcionalidad del filtro. Los coeficientes del filtro serán cuantificados y redondeados a través del software MatLab.

Figura 3. 1: Tarjeta de entrenamiento de sistemas digitales Altera DE2. Elaborado por: Autor

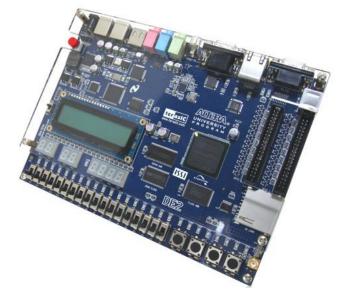

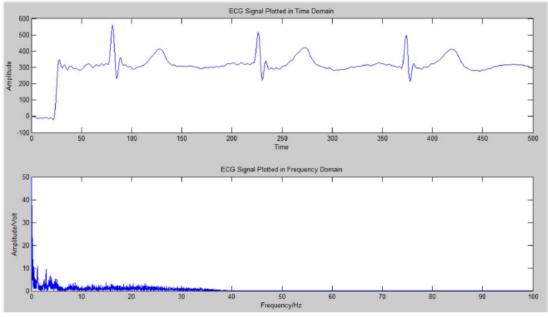

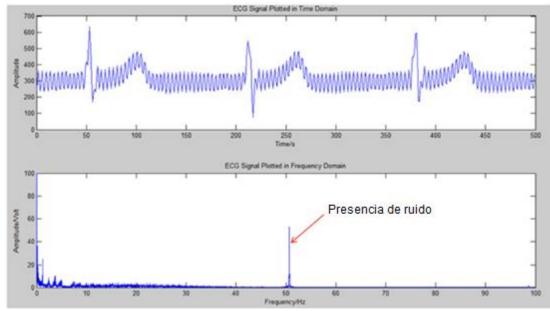

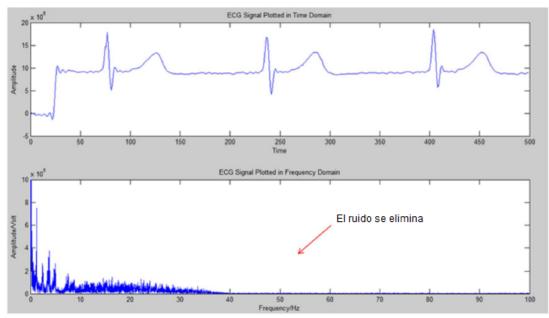

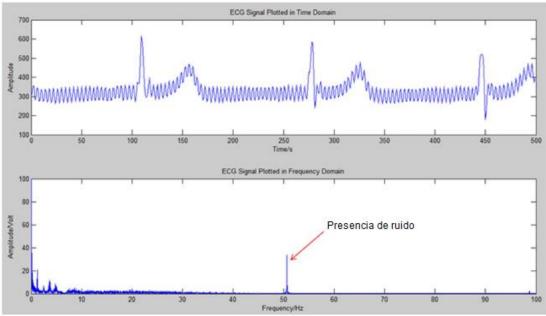

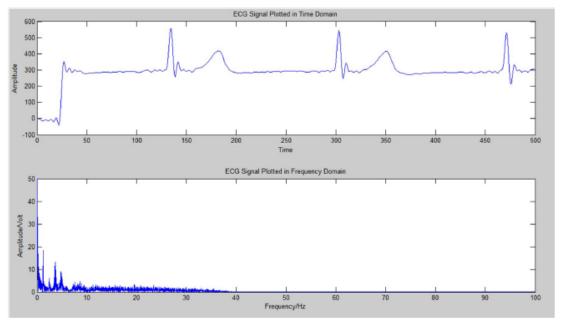

# 3.2. Señal ECG con filtrado digital FIR pasa bajo usando MatLab.

En la figura 3.2, la señal ECG se representa gráficamente tanto en el dominio del tiempo como en el dominio de la frecuencia. Es más fácil analizar la región del ruido de una señal trazándola en el dominio de la frecuencia. La

señal ECG se filtra utilizando un filtro digital de respuesta finita al impulso (Finite Impulse Response, FIR) pasa bajo previamente diseñado en la plataforma de MatLab.

Figura 3. 2: Señal ECG con ruido trazado en el dominio del tiempo y la frecuencia. Elaborado por: Autor

Figura 3. 3: Señal de ECG filtrada usando MATLAB. Elaborado por: Autor

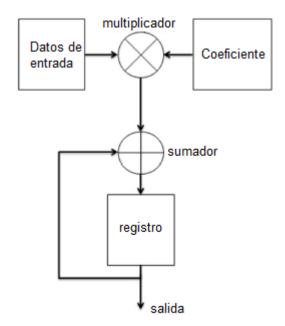

### 3.3. Diseño de la unidad de datos.

La función principal de la unidad de datos es realizar el procesamiento de datos y su respectivo cálculo. El diseño del hardware del diseño del filtro FIR puede deducirse de la siguiente ecuación:

$$y[n] = a_0x[n] + a_1x[n-1] + a_2x[n-2] + \dots + a_{49}x[n-49]$$

$$y[n] = salida$$

$$n = num\acute{e}ro\ de\ datos\ de\ entrada$$

$$a_i = coeficiente, i = 0,1,2,...,50$$

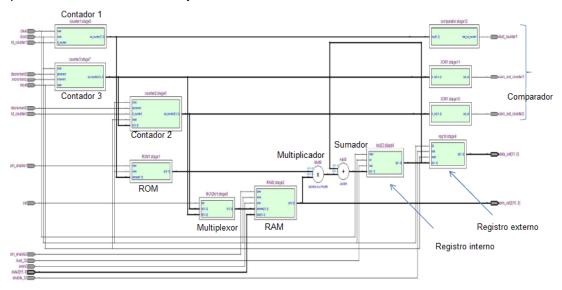

Es obvio que, a partir de la ecuación anterior, el filtro FIR se está multiplicando y agregando todo el tiempo. Para diseñar la unidad de datos, se utiliza un multiplicador, un sumador y los registros para implementar el filtro FIR. En la figura 3.4 se muestra el diagrama de bloques funcional del filtro digital FIR.

Figura 3. 4: Diagrama de bloques funcionales para la arquitectura del filtro FIR. Elaborado por: Autor

Para el presente trabajo se utiliza una memoria ROM para almacenar los coeficientes del filtro, ya que los valores son siempre constantes. Para los datos de entrada de la señal ECG, se utiliza una memoria RAM con un tamaño

de palabra de 16k. El sumador y multiplicador indicado en este diseño se aplica desde el módulo predefinido en la plataforma de simulación de Quartus II de Altera.

El tamaño del ancho para los datos de entrada y el coeficiente es de 16 bits, respectivamente. Pero el tamaño de ancho para el multiplicador y el sumador será de 32 bits. La señal ECG utilizada para ser filtrada sólo contenía 10 bits. Por lo tanto, los registros de salida con el ancho de 32 bits son suficiente para superar el problema de desbordamiento.

En la figura 3.5 se muestra el diagrama de bloques de la unidad de datos que se codificó utilizando el lenguaje de programación VHDL y se sintetizó a partir del software Quartus II. Las memorias ROM y RAM se utilizan para almacenar coeficientes y datos de la señal ECG, respectivamente, antes de que se inicie cualquier procesamiento de datos. El ancho de entrada y salida para las memorias RAM y ROM es de 16 bits.

Figura 3. 5: El diagrama de bloques de la unidad de datos para el filtro FIR pasa bajo sintetizado en Quartus II.

Elaborado por: Autor

Este trabajo también se va utilizar registros, contadores, memorias RAM y ROM con una señal de reloj síncrono. Dos registros con ancho de 32 bits se

utilizan en la etapa de salida debido al registro interno que se borrará cuando el cálculo de los datos de entrada se realiza una vez. Al mismo tiempo, el contador 1 se borrará también. Por lo tanto, se requiere otro registro para contener los datos de salida. En otras palabras, el registro interno tendrá una señal asíncrona diferente de otro registro y de los contadores. Otros elementos lógicos tales como contadores, comparadores y multiplexores se utilizan para controlar señales.

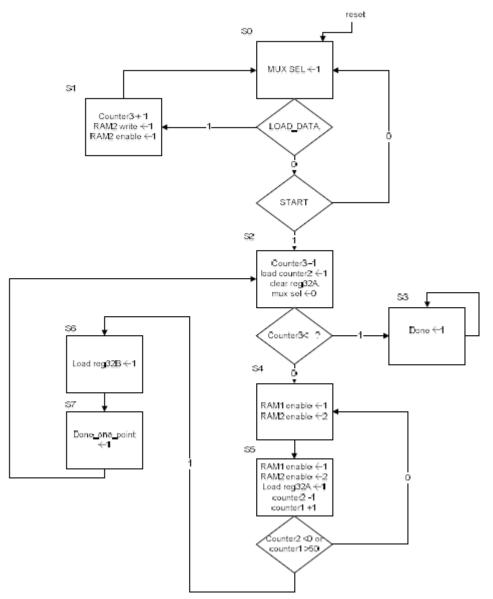

#### 3.4. Diseño de la unidad de control.

Para determinar la secuencia de la operación de procesamiento de datos realizada por la unidad de datos, se necesita una unidad de control. La unidad de control funciona para entregar las señales de control en el orden especificado. Para el diseño del filtro FIR, una unidad de datos requiere otros elementos lógicos juntos para controlar la secuencia de cálculo de datos. Se necesita un multiplexor, tres contadores y tres comparadores. Existen otras señales de control externas tales como señal de inicio y señal de datos de carga para configurar la unidad de control.

Los contadores se utilizan para contar el número total de datos de entrada y apuntar las direcciones de las memorias ROM y RAM. Los comparadores se utilizan para determinar en qué situación el procesamiento de datos debe comenzar, detenerse o continuar. La secuencia general para el filtro FIR se muestra en la figura 3.4. Se desarrolla una tabla vectorial (véase tabla 3.1) de control que muestra las señales activadas en cada estado.

Inicialmente, los datos de entrada se almacenarán en una memoria RAM (véase la figura 3.6) antes de que comience cualquier cálculo de datos. El contador 3 es un contador que se utiliza para acumular la cantidad total de datos de entrada y determinar si se calculan todos los datos de la señal ECG de entrada. Una vez que todos los datos de entrada están listos, se dará la señal de inicio a la unidad de datos para comenzar el cálculo de datos.

Figura 3. 6: Gráfico de ASM para el diseño del filtro FIR pasa bajo. Elaborado por: Autor

Las señales de incremento y decremento se aplican a los contadores apropiados para actualizar las direcciones de las memorias RAM y ROM. Esto es para asegurar que el procesamiento de datos para señales ECG pueda continuar. Cuando se completa un punto de los datos de salida, se cargará en los registros externos y se mostrará una señal de un punto. Una señal hecha será entregada si y sólo si todos los datos de entrada se calculan o cuando el valor del contador 3 es menor que cero.

Tabla 3. 1: Señales vectoriales de control activadas y desactivadas.

| Estado Operación Control Vector |                                                                  |       |                    |       |   |                |               |               |     |       |                 |                 |              |                 |                 |

|---------------------------------|------------------------------------------------------------------|-------|--------------------|-------|---|----------------|---------------|---------------|-----|-------|-----------------|-----------------|--------------|-----------------|-----------------|

|                                 |                                                                  | hecho | Done_one_<br>point | claro |   | Ram_<br>enable | Carga reg32 A | Carga reg32 B | Sel | Wren2 | Ld_<br>counter1 | Ld_<br>counter2 | Incremento 3 | Decremento<br>2 | Decremento<br>3 |

| S0                              |                                                                  | 0     | 0                  | 0     | 0 | 0              | 0             | 0             | 1   | 0     | 0               | 0               | 0            | 0               | 0               |

| S1                              | Counter3 +1  RAM2 write←1  RAM2 enable←1                         | 0     | 0                  | 0     | 0 | 1              | 0             | 0             | 1   | 1     | 0               | 0               | 1            | 0               | 0               |

| \$2                             | Counter3-1 load counter2←1 clear←1 mux sel←0                     | 0     | 0                  | 1     | 0 | 0              | 0             | 0             | 0   | 0     | 0               | 1               | 0            | 0               | 1               |

| <b>S</b> 3                      | Done←1                                                           | 1     | 0                  | 0     | 0 | 0              | 0             | 0             | 0   | 0     | 0               | 0               | 0            | 0               | 0               |

| S4                              | Rom1 enable←1<br>Ram2 enable←1                                   | 0     | 0                  | 0     | 1 | 1              | 0             | 0             | 0   | 0     | 0               | 0               | 0            | 0               | 0               |

| \$5                             | Rom1 enable←1 Ram2 enable←1 Load reg32A←1 Counter2 -1 Counter1+1 | 0     | 0                  | 0     | 1 | 1              | 1             | 0             | 0   | 0     | 1               | 0               | 0            | 1               | 0               |

| S6                              | Load reg32B ←1                                                   | 0     | 0                  | 0     | 0 | 0              | 0             | 1             | 0   | 0     | 0               | 0               | 0            | 0               | 0               |

| <b>S</b> 7                      | Done_one_point←1                                                 | 0     | 1                  | 0     | 0 | 0              | 0             | 0             | 0   | 0     | 0               | 0               | 0            | 0               | 0               |

Elaborado por: Autor

## 3.5. Diseño de interfaz.

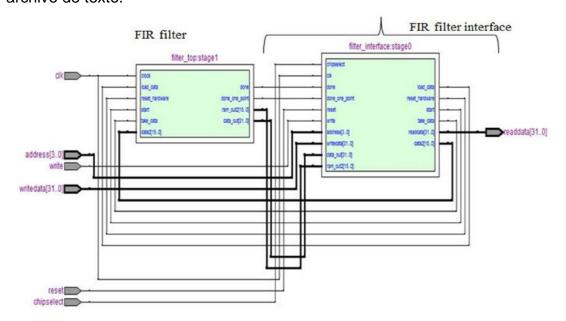

Con el fin de leer y escribir interfaces en los componentes tanto maestro como esclavo en un sistema de memoria mapeada, se utiliza una interfaz de memoria mapeada Avalon (MMA). Estos componentes incluyen microprocesadores, memorias, UART, DMA y temporizadores que se conectan con un tejido de interconexión.

El tejido interconectado del sistema es una estructura de interconexión de alto ancho de banda para conectar componentes que utilizan memorias mapeadas Avalon (MMA). Para el diseño de la interfaz, algunas señales son fijas e inalterables. Las señales incluyen las señales de reinicio, de reloj, de selección de chip, de dirección, de escritura, de escritura/datos y de lectura/datos.

Es lo mismo si se aplica MMA al filtro de paso bajo FIR diseñado. En la figura 3.7, se muestra la conexión entre el filtro FIR y el tejido de interconexión del sistema. Para obtener datos del hardware o ingresar cualquier dato al hardware, se utilizarán buses de lectura/datos y escritura/datos,

respectivamente. En este diseño los datos sin procesar de la señal ECG pasarán a través del firmware vía bus de escritura/datos al hardware y almacenados en la memoria RAM. Los datos de la señal ECG filtrados se pasarán a través del bus lectura/datos al firmware y se almacenarán en un archivo de texto.

Figura 3. 7: Diagrama de bloques de la conexión entre el filtro FIR pasa bajo con la interconexión del sistema.

Elaborado por: Autor

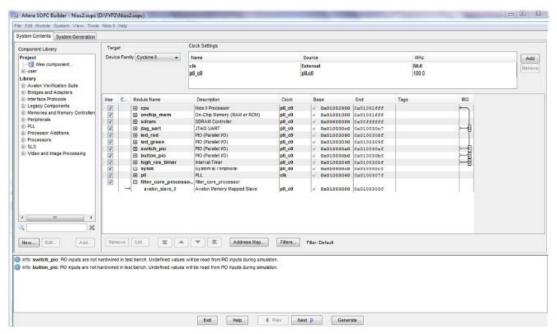

# 3.6. Sistema en chip programable (SOPC).

El Nios II de Altera es un procesador que se puede implementar en dispositivos FPGA usando Quartus. Para implementar un sistema útil o utilizar el procesador Nios II en la placa DE2, es necesario añadir otras unidades funcionales tales como memorias, interfaces de entrada y salida e interfaces de comunicación. Por lo tanto, un sistema compatible en el chip programable es necesario para esta tarea. El sistema SOPC Builder será variado, ya que depende del requisito de un proyecto individual.

SOPC Builder conecta los componentes soft-hardware creando un sistema completo que se ejecuta en la placa FPGA de Altera. Los componentes predefinidos en SOPC Builder incluyen memoria SDRAM,

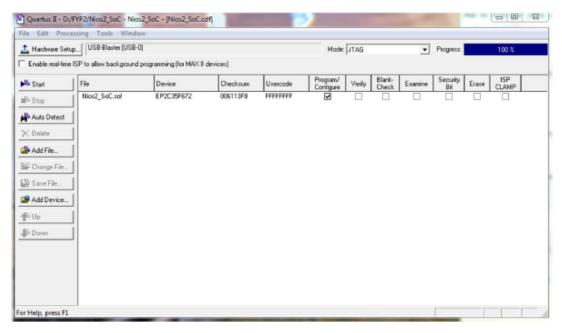

memoria on-chip, LEDs, interruptores, temporizadores, JTAG UART y así sucesivamente. Las interconexiones de estos componentes están conectadas a través del bus Avalon. En la figura 3.8, se muestra el Altera SOPC Builder que se utilizará en este diseño de filtro FIR. El hardware de filtro FIR diseñado se trata como un componente que se agregará en SOPC Builder. Antes de generar el SOPC Builder, es importante asignar automáticamente la dirección base y las IRQ de todos los componentes. Un sencillo sistema integrado Nios II está construido con algunos periféricos como procesador Nios II, periféricos de identificación del sistema, memoria en chip, SDRAM, PLL (generación de señal de reloj), 18 LEDs rojos, 8 LEDs verdes, temporizadores y JART UART para comunicación de datos.

Se generará un archivo de sistema cuando la generación del SOPC Builder tenga éxito. El archivo del sistema <<.ptf>> se descargará en la placa Altera FPGA DE2 a través de Quartus II utilizando cable USB. En la figura 3.9 se muestra el proceso de descarga del filtro FIR pasa bajo diseñado en la placa. La barra de progreso muestra 100% cuando se completa la descarga.

Figura 3. 8: Ventana principal de Altera SOPC Builder. Elaborado por: Autor

Figura 3. 9: Descarga de programación en Quartus II para el filtro FIR pasa bajo en FPGA DE2 de Altera.

Elaborado por: Autor

# 3.7. Diseño del Firmware.

El entorno de desarrollo integrado (IDE) de Altera Nios II se utiliza para diseñar el firmware deseado para el filtro FIR pasa bajo. Para acceder a los registros en la lógica del usuario, se utilizan las macros IORD () y IOWR (). El macro IORD lee los datos del hardware mientras IOWR proporciona datos de entrada al hardware. Los datos de las señales ECG se almacenan en un archivo de texto.

La longitud de datos preestablecida de la señal ECG es 10000. Por lo tanto, es imposible para un usuario introducir los datos uno a uno en el hardware. Un enfoque para resolver este problema es leer los datos de archivo de texto y almacenar en una matriz a través del firmware. Los datos de la señal ECG pasarán del firmware al tablero. Una vez finalizado el proceso de filtrado, los datos de salida deben recuperarse y almacenarse de nuevo en el archivo de texto para su verificación. Para lograr esta tarea, se utiliza el sistema de archivos basado en host. El sistema de archivos basado en host permite a los

programas que se ejecutan en una placa de destino, leer y escribir archivos almacenados en la computadora host.

El NIOS II IDE transmite datos de archivo a través del cable blaster USB. Se puede acceder al sistema de archivos basado en el host utilizando las funciones estándar de E / S de la biblioteca, como fopen (), fscanf (), fclose () y fprintf (). El sistema de archivos basado en host es un componente de software que se debe agregar a la biblioteca del sistema.

Hay algunas desventajas del sistema de archivos basado en host. En primer lugar, sólo puede funcionar mientras se depura un proyecto. No se puede utilizar para sesiones de ejecución. Los datos de los archivos de host viajan entre el host y el destino en serie a través del cable de descarga de Altera. Por lo tanto, el tiempo de acceso a archivos es bastante lento. Se tarda aproximadamente 10 ms por llamada al host. Es indudable que es obligatorio especificar el punto de montaje dentro del sistema de archivos HAL para que el archivo sea leído o escrito.

Un código simple se está abriendo un archivo que tiene acceso al sistema host. Por lo tanto, los datos de entrada de la señal de ECG se pueden leer fácilmente desde el host y la salida de la señal de ECG después de filtrado se puede volver a escribir convenientemente al sistema de archivos de host. Los datos de ECG filtrados almacenados en un archivo de texto pueden usarse para verificar la funcionalidad del filtro de paso bajo FIR. La herramienta MATLAB se utiliza para trazar la señal de ECG filtrada para analizar la señal.

#### 3.8. Resultados obtenidos.

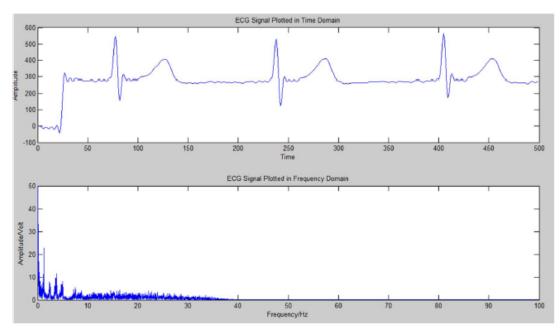

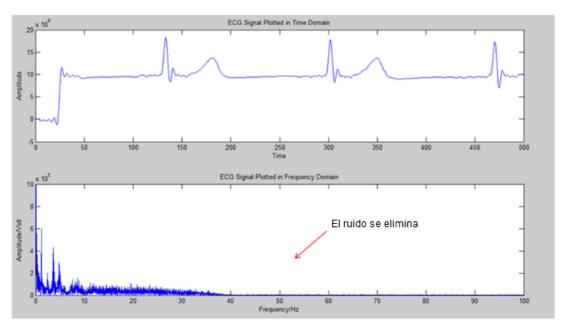

## 3.8.1. Datos de entrada.

Los datos de entrada de la señal ECG se leen directamente desde el sistema de archivos basado en host. El procesamiento de datos de la señal

se realiza dentro de la placa para eliminar el ruido no deseado en la señal original. Toda la longitud de los datos de la señal ECG se establece en 10000.

Figura 3. 10: Muestra 1 de la señal bruta ECG. Elaborado por: Autor

Figura 3. 11: Señal ECG filtrada utilizando la placa FPGA DE2 de Altera. Elaborado por: Autor

Figura 3. 12: Señal ECG filtrada usando MATLAB. Elaborado por: El Autor

Figura 3. 13: Muestra 2 de la señal ECG. Elaborado por: El Autor

Figura 3. 14: Señal de ECG filtrada utilizando la placa FPGA DE2 de Altera. Elaborado por: El Autor

Figura 3. 15: Señal ECG filtrada usando MATLAB. Elaborado por: El Autor

# 3.8.2. Comparación de señales ECG.

De las figuras 3.11 y 3.14, es muy obvio que las señales ECG son filtradas con éxito. Las señales ECG que se filtran usando la placa FPGA DE2 Altera se representan tanto en el dominio de tiempo como en el dominio de la

frecuencia utilizando el software MatLab. Para asegurar que las señales ECG filtradas del hardware son correctas, las mismas señales crudas de ECG se filtran nuevamente utilizando MatLab. Se traza la señal ECG filtrada utilizando tanto hardware (DE2 de Altera) y software (MatLab). Se puede resumir que el filtro FIR pasa bajo está funcionando bien. Puede filtrar el ruido en la señal sin procesar el ECG y da una salida similar si es comparada a la salida de MatLab.

Si se miran los datos de las señales ECG filtradas, hay ligeras diferencias entre las señales de ECG filtradas utilizando la placa de entrenamiento FPGA DE2 de Altera y la herramienta de simulación MatLab. Esto se debe a la cuantificación del coeficiente de filtro desde longitud de palabra infinita hasta longitud de palabra finita.

Los coeficientes de filtro se convierten y se redondean debido a restricciones de hardware. Sin embargo, a partir del trazado de señales ECG en el dominio del tiempo, muestra que el filtro funciona como se esperaba a través del efecto de cuantificación. El presente trabajo de titulación, el efecto de cuantificación no es un impacto.

#### 3.8.3. Limitaciones de hardware.

Hay algunas limitaciones de hardware en el presente trabajo. En primer lugar, los coeficientes de filtros obtenidos de MatLab están en forma de punto flotante. Aunque, MatLab puede tener una precisión muy alta. Para obtener la misma señal de salida ECG del dispositivo DE2 de Altera con la salida de MatLab, es esencial utilizar la longitud de palabra infinita para los coeficientes.

Sin embargo, no es práctico cuando se trata de implementación de hardware. Para implementar una longitud de palabra infinita de coeficientes del filtrado, se perderá muchos recursos de hardware (DE2 de Altera). Por lo tanto, es necesario modificar y redondear el número de punto flotante del coeficiente de filtro en forma entera.

Los coeficientes del filtro son modificados, para lo cual tendrán precisiones de bits ligeramente inferiores si se comparan con los coeficientes del filtro original. Esto se debe a que los coeficientes de filtrado se cuantifican desde longitud de palabra infinita hasta longitud de palabra finita. Aparte de eso, el chip Cyclone II integrada en la tarjeta DE2 de Altera tiene un bloqueo de memoria muy limitado. Al diseñar el filtro FIR, hay que hacer muchas consideraciones. En este diseño, la memoria RAM se utiliza para almacenar las señales sin procesar del ECG. El tamaño de la memoria RAM está limitado a 16k palabra. Esto se debe principalmente a la limitación del bloque de memoria de Cyclone II. Por lo tanto, la longitud de datos de la señal de ECG no puede ser mayor de 16k.

## Conclusiones

- Fueron descritas las bases teóricas de señales ECG y la tecnología FPGA cuya importancia fue muy relevante para el desarrollo del trabajo de titulación.

- 2. Para el desarrollo del filtro digital FIR pasa bajo se utilizó la herramienta FDA de MatLab y Quartus II de Altera, para eliminación del ruido en la señal ECG mediante la tarjeta FPGA DE2 de Altera, la misma que permite procesar la información de manera eficiente, por tanto, se pudo satisfacer las expectativas planteadas en los objetivos específicos.

- Los resultados obtenidos durante la ejecución, indican que el filtrado se generado en la tarjeta FPGA elimina totalmente el ruido generado en la adquisición de las señales ECG.

# Recomendaciones

- Desarrollar algoritmos para disminución de ruido en el procesamiento de señales ECG mediante filtros digitales FIR.

- 2. Desarrollar una interfaz gráfica en LabView para el procesamiento de señales ECG usando los diferentes filtros digitales FIR.

# **Bibliografia**

- Aequum. (2016). Bradicardia en adolescentes. Recuperado el 1 de febrero de 2017, a partir de https://www.aequum.pro/bradicardia-en-adolescentes.html

- Blazquez D., C. (2017). Sistema Cardiovascular [Página personal].

Recuperado el 30 de enero de 2017, a partir de https://www.uv.mx/personal/cblazquez/files/2012/01/Sistema-Cardiovascular.pdf

- Cardona, P. A., Mayoral, V., & Muñoz, P. A. (2010). Sistema para la adquisición de señales electrocardiográficas Usando Matlab®. *Scientia Et Technica*, *16*(44), 304–309.

- Chu, P. P. (2008). FPGA prototyping by VHDL examples: Xilinx Spartan-3 version. Hoboken, N.J. Wiley-Interscience.

- Dupre, A., Vieau, S., & Iaizzo, P. A. (2009). Basic ECG Theory, 12-Lead

Recordings and Their Interpretation. En P. A. Iaizzo (Ed.), *Handbook of Cardiac Anatomy, Physiology, and Devices* (pp. 257–269). Totowa, NJ:

Humana Press. Recuperado a partir de http://link.springer.com/10.1007/978-1-60327-372-5\_17

- Herrera L., J. C., & González R., J. C. (2015). Tecnologías programables.

Recuperado el 1 de febrero de 2017, a partir de http://embebidos-cidetec.com.mx/profesores/jcrls/doctos/fpga\_jchl.pdf

- Jaber, H., & Cankaya, I. (2015). Heart Rate Monitoring and PQRST Detection

Based on Graphical User Interface with Matlab. *International Journal of Information and Electronics Engineering*, *5*(4), 311–316.

- Jagadiswara R., B., & Usharani, A. (2013). Enhancement of ECG Signal by using Digital FIR Filter. *International Journal of Science and Research*, *4*(2), 910–913.

- Karris, S. T. (2005). *Digital circuit design with an introduction to CPLDs and FPGAs*. Fremont, Calif.: Orchard Publications. Recuperado a partir de http://www.books24x7.com/marc.asp?bookid=9658

- Larroza S., A. M., Zena G., V., & Frutos O., L. (2008). Monitor electrocardiográfico con tecnología inalámbrica ZigBee. *Conciencia Tecnológica*, (36), 50–56.

- López Farré, A., & Macaya Miguel, C. (2009). Libro de la salud cardiovascular del Hospital Clínico San Carlos y de la Fundación BBVA. Bilbao: Fundación BBVA. Recuperado a partir de http://public.eblib.com/choice/publicfullrecord.aspx?p=4422194

- Mamatha, B., & Ramachandram, V. (2012). Design and implementation of 120 order FIR filter based on FPGA. *International Journal of Engineering Sciences & Emerging Technologies*, *3*(1), 90–97.

- Mbachu, C. B., & Offor, K. J. (2013). Reduction of powerline noise in ECG signal using FIR digital filter implemented with hamming window.

International Journal of Science Environment and Technology, 2(6), 1380–1387.