# UNIVERSIDAD CATOLICA DE SANTIAGO DE GUAYAQUIL

Facultad de Educación Técnica para el

Desarrollo

## Tesis de Grado

Previo a la Obtención del título de: Ingeniería en Telecomunicaciones

Mención: "Gestión Empresarial"

#### Tema:

Diseño e Implementación de un filtro digital (FIR) orientado al uso del laboratorio de procesamiento de señales digitales (PSD)

## Realizado por:

Amaguaya Colcha Verónica

Burgos Acosta Luis

Espinoza Espinosa Byron

Fernández De La S Jorge

Nivela Villarroel Nadia

Torres Tobar Mildred

## Director

Ing. Marcos Andrade

Guayaquil – Ecuador 2010 – 2011

## **TESIS DE GRADO**

## **Titulo**

Presentado a la Facultad Tecnica, Escuela de Ingeniería en Telecomunicaciones de la Universidad Católica Santiago de Guayaquil por:

> Amaguaya Colcha Verónica Burgos Acosta Luis Espinoza Espinosa Byron Fernández de la S Jorge Nivela Villarroel Nadia Torres Tobar Mildred

Para dar cumplimiento con uno de los requisitos para optar por el titulo de:

Ingeniería en Telecomunicaciones

Mención: "Gestión Empresarial"

## Miembros del tribunal:

Ing. Héctor Cedeño Abad

Ing. Pedro Tutivén López

Ing. Marcos Andrade Reyes

Ing. Efraín Suárez Murillo

Ing. Washington Medina Moreira

Ing. Elías Andrade Díaz

Ing. Víctor del Valle Ramos

Dr. Kléber López Parrales

## **AGRADECIMIENTOS**

Agradecemos sinceramente:

Agradeciendo primeramente a nuestro Dios, quien nos da la vida y nos da fuerzas para seguir adelante, a nuestros padres quienes a lo largo de nuestras vida nos ha apoyado y motivado nuestra formación académica, creyeron en nosotros en todo momento y no dudaron de nuestras habilidades.

A nuestros profesores a quienes les debemos gran parte de nuestros conocimientos, gracias a su paciencia, enseñanza y finalmente un eterno agradecimiento a la prestigiosa universidad la cual abre sus puertas a jóvenes como nosotros, preparándonos para un futuro competitivo y formándonos como personas de bien.

Al ingeniero Marco Andrade, nuestro profesor, tutor y amigo, por su apoyo y conocimientos durante toda la tesis.

Al ingeniero Efraín Suarez, por su apoyo en todo momento durante toda nuestra tesis.

Esperamos, por el bien de la enseñanza, que pronto podamos contar con la mejor formación diseñando y ejecutando proyectos.

## **DEDICATORIAS**

Dedico esta tesis a mi Dios, quien me dio la sabiduría e inteligencia al nacer.

A mis padres, quienes me apoyaron y confiaron en mi en todo momento.

A mi esposo e hijo, quienes han sido la inspiración y motivación para mi superación profesional. (Verónica)

Esta tesis es una parte de mi vida y comienzo de otras etapas por esto y más se la dedico a toda mi familia que siempre estuvo apoyándome en el trayecto de mi formación académica. (Luis)

Dedico a mis padres, por ser quienes velaron por mí en todo el trayecto universitario, y que me apoyaron en mi formación académica. (Nadia)

Dedico ante todo a Dios, por iluminar mi vida y darme fuerzas. A mis padres por su apoyo, paciencia y amor incondicional en todo momento. (Jorge)

A mi familia, por creer en mi y darme su apoyo en toda mi vida universitaria, quienes con su amor y dedicación me ayudaron a cumplir mis metas propuestas.

(Byron)

Dedico este trabajo de Tesis aun ser omnipotente nuestro padre celestial q por medio de mis padres me ha dado la fortaleza y los recursos para poder culminar este trabajo. A mi madre y mejor amiga Rossy Tobar a mi padre Mario Torres y a mis hermanos Masiu y Judy . (Mildred)

## **PROLOGO**

El presente trabajo se realizó con la finalidad de ser expuesto ante un jurado como tema de tesis para obtener el título de Ingeniería en Telecomunicaciones con Mención en Gestión Empresarial.

La elección del tema se hizo tomando en cuenta la necesidad de los estudiantes cuyos intereses y motivaciones van orientándose al diseño de proyectos utilizando tarjetas especializadas como es el caso de la Spartan 3E, en esta tesis se presenta dicha tarjeta y a su vez se explica el diseño de un filtro Digital (FIR) implementado en la FPGA (Spartan 3E de Xilinx), consta principalmente de periféricos conocidos por la totalidad de los usuarios; puertos VGA para la conexión de un monitor, PS2 para teclados, USBs, Ethernet, etc.

El diseño se realiza en un software que calcula los coeficientes del filtro y la reconfiguración del hardware. Para ello se considero la necesidad del estudiante a una mejor comprensión mediante la práctica, sin quedar dudas al respecto de la materia dada.

En esta tesis también se destaca principalmente la realización de prácticas debidamente documentadas para el aprendizaje y sobre todo el acercamiento al alumno con los dispositivos de lógica difusa que actualmente copan el mercado de las comunicaciones y la información. Siempre se mantuvo una visión general con la idea de presentar un proyecto que permita la interrelación de los estudiantes con la práctica y no quedar solo en teoría, ya que esto nos ayudara que la explicación sea más entendible.

## **RESUMEN**

Antiguamente el diseño e implementación de un sistema digital complejo era muy tedioso y podría llevar mucho tiempo desde su inicio hasta su culminación.

Hoy en día con la aparición de las herramientas de síntesis y simulación los ingenieros especializados pueden terminar un diseño en corto tiempo disminuyendo costos y aumentando la productividad.

En este trabajo se muestra el diseño de un analizador lógico implementado en un FPGA utilizando como entrada de diseño VHDL.

La herramienta de síntesis y simulación que se utilizo fue el ISE 10.1 y pertenece a la empresa líder en lógica programable XILINX.

Entre sus características podemos mencionar la reducción de tamaño y costo, además de facilitar el diseño de sistemas complejos y el tiempo de diseño se reduce en gran medida.

Con esto el producto se puede enviar al campo de trabajo en poco tiempo y modificarlo si así se requiere, ya que un gran número de ellos son reprogramables

## **ANTECEDENTES**

Como ya se mencionó en líneas anteriores, es gracias al avance de las computadoras modernas que el tratamiento digital de señales se ha expandido y se ha hecho cada vez más fuerte. Han contribuido con su velocidad al montaje de algoritmos de procesamiento para lograr entregar respuestas casi instantáneas, siempre dentro de los límites exigidos por el desarrollo en las diferentes aplicaciones en que han sido utilizadas.

Las computadoras no sólo han influido en el montaje de algoritmos, además se han convertido en una herramienta fundamental para los diseñadores, ya que gracias a éstos se ha conseguido elaborar mejores y variados algoritmos para el diseño de filtros y herramientas de proceso.

El diseño de filtros se ha apoyado en los dispositivos lógicos programables, los cuales han jugado un papel muy importante en el montaje de los filtros digitales, puesto que gracias a ellos se ha logrado un adecuado funcionamiento en tiempo real. El FPGA es uno de estos dispositivos, que posee la cualidad de reconfiguración, lo que permite realizar cambios en la arquitectura sin necesidad de producir variaciones en el montaje o en el software que se está operando, ya que existe todo esto gracias al desarrollo industrial y avances tecnológicos.

## ÍNDICE GENERAL

AGRADECIMIENTOS DEDICATORIAS PROLOGO RESUMEN ANTECEDENTES

INTRODUCCION

1

50

## CAPITULO 1

## 1. FILTRO DIGITAL

2.

| 1.1.  | INTRODUCCIÓN AL DISEÑO DE FILTROS DIGITALES                       | 3  |

|-------|-------------------------------------------------------------------|----|

| 1.2.  | MECANISMO DEL PROCESAMIENTO DEL FILTRO DIGITAL                    | 4  |

| 1.3.  | TIPOS DE FILTROS                                                  | 5  |

|       | 1.3.1. De acuerdo a la ganancia                                   | 7  |

|       | 1.3.2. De acuerdo a su respuesta de frecuencia                    | 8  |

|       | 1.3.3. De acuerdo al método de diseño                             | 14 |

|       | 1.3.4. De acuerdo a su aplicación                                 | 19 |

|       | 1.3.5. Otros tipos                                                | 19 |

| 1.4.  | IMPORTANCIA EN PROCESAMIENTO DIGITAL DE SEÑALES                   | 26 |

|       | 1.4.1. Que es DSP                                                 | 26 |

|       | 1.4.2. Aplicaciones de DSP                                        | 28 |

|       | 1.4.3. Importancias de las transformadas en el DSP                | 28 |

|       | 1.4.4. Arquitectura                                               | 29 |

|       | 1.4.5. Arquitecturas Estándar en el DSP                           | 30 |

|       |                                                                   | 50 |

|       |                                                                   |    |

| CAP   | PITULO 2                                                          |    |

|       |                                                                   |    |

|       | RRAMIENTAS PARA EL FPGA Y SU ENTORNO DE DESARROLLO                | 31 |

| 2.1.  | ELEMENTOS QUE CONFORMAN LOS FPGAS DE XILINX                       | 32 |

| 2.2.  | CARACTERISTICAS DE LA FPGA                                        | 34 |

| 2.3.  | PROGRAMACION FPGA                                                 | 35 |

| 2.4.  | TECNOLOGIA DE LA MEMORIA DE PROGRAMACION                          | 36 |

| 2.5.  | FORMAS DE ALMACENAR LOS VALORES(BITSTREAM)                        | 37 |

|       | EN LA MEMORIA                                                     |    |

| 2.6.  | FABRICANTES DE DISPOSITIVOS DE FPGA                               | 39 |

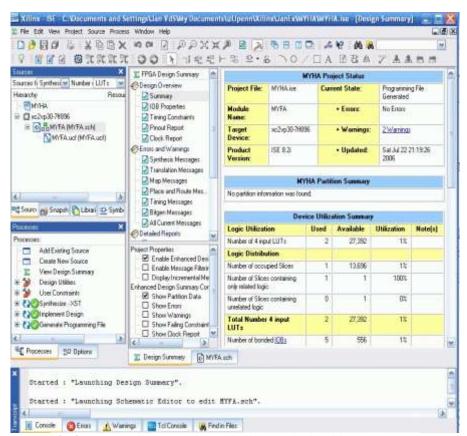

| 2.7.  | EL ENTORNO DE PROGRAMACION ISE DESIGN SUITE DE XILINX             | 40 |

| 2.8.  | DISENO DE FLUJO NATURAL                                           | 40 |

|       | 2.8.1. Diseño de entrada                                          | 41 |

|       | 2.8.2. La síntesis                                                | 41 |

|       | 2.8.3. Verificación ( Simulation)                                 | 42 |

|       | 2.8.4. Implementación                                             | 42 |

|       | 2.8.5. Configuración de dispositivos                              | 43 |

|       | 2.8.6. La ventana del explorador de proyectos (Proyect Navigator) | 43 |

|       | 2.8.7. La ventana de fuentes (Sources)                            | 44 |

|       | 2.8.8. La ventana de procesos (Processes)                         | 44 |

| 2.9.  | INTRODUCCION A MATLAB Y SIMULINK                                  | 44 |

|       | 2.9.1. Desarrollo de aplicaciones utilizando                      | 45 |

|       | Matlab en FPGA                                                    |    |

|       | 2.9.2. Componentes de Matlab                                      | 46 |

| 2.10. | SIMULINK                                                          | 47 |

|       | 2.10.1. El Entorno del Trabajo de Simulink                        | 47 |

| 2.11. | SISTEMA DE CONTROL DE LA CAJA DE HERRAMIENTAS (CONTROL            | 48 |

|       | SYSTEM TOOLBOX )                                                  | 49 |

|       | 2.11.1. Características principales de la Caja De Herramientas    | ., |

|       | 2.11.2. Usos de La Caja De Herramientas                           | 49 |

| 2.12. | Aplicaciones de la FPGA                                           | 50 |

## **CAPITULO 3**

| 3. | FILTRO DIGITAL FIR                                                                   |            |

|----|--------------------------------------------------------------------------------------|------------|

|    | 3.1. QUE ES UN FILTRO DIGITAL FIR                                                    | 51         |

|    | 3.2. ESTRUCTURA DEL FILTRO FIR                                                       | 52         |

|    | 3.3. POLOS Y CEROS DEL FILTRO FIR                                                    | 53         |

|    | 3.4. DISEÑO DEL FILTRO FIR                                                           | 53         |

|    | 3.5. CARACTERISTICAS DEL FILTRO FIR                                                  | 54         |

|    | 3.6. TIPOS DE FILTRO                                                                 | 54         |

|    | 3.7. IMPLEMENTACION DE FILTROS DIGITALES TIPO FIR EN FPGA                            | 55         |

|    | 3.7.1. Factores de implementación                                                    | 57         |

|    | 3.7.2. Implementación en el FPGA                                                     | 57         |

|    | 3.7.3. Identidades                                                                   | 58         |

|    | 3.7.4. La Arquitectura del Filtro FIR                                                | 59         |

|    | 3.7.5. Pipeline del Filtro FIR                                                       | 60         |

| 4. | CONCLUSIONES                                                                         | 62         |

| 5. | RECOMENDACIONES                                                                      | 65         |

| 6. | GLOSARIO                                                                             | 66         |

| 7. | BIBLIOGRAFÍA                                                                         | 69         |

| 8. | ANEXOS                                                                               | 70         |

| A. | 7.1 PRACTICA UNO: USANDO SIMULINK                                                    | 71         |

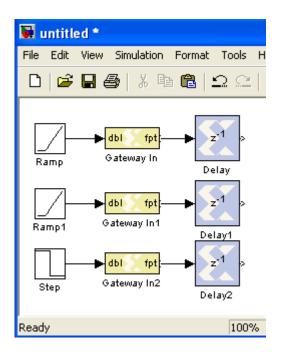

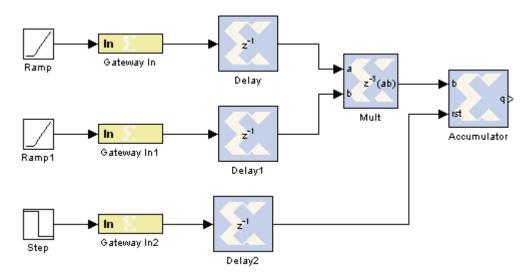

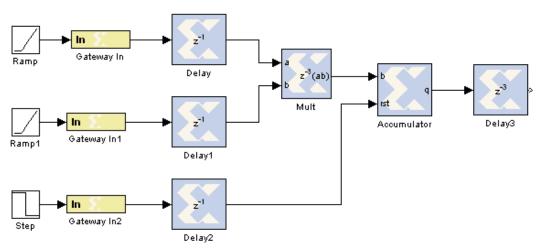

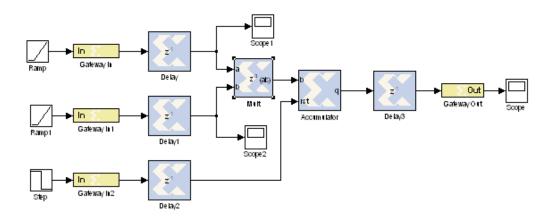

|    | A7.1.1 Crear un diseño simple                                                        | 76         |

|    | A.7.1.2 Analizando el efecto del periodo del muestreo                                | 77         |

|    | A.7.1.3 Cree un diseño simple usando los bloques de Simulink                         | 79         |

|    | A.7.1.4 Crear un subsistema                                                          | 80         |

|    | A.7.1.5 Conclusiones                                                                 | 81         |

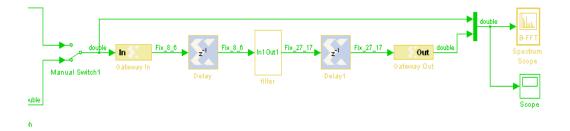

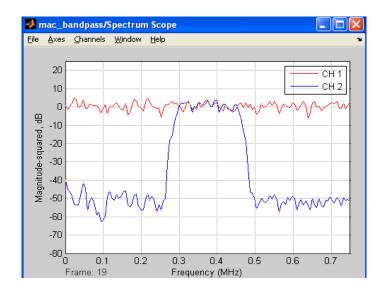

|    | A.7.2 PRACTICA DOS: CREACIÓN DE UN MAC 12 X 8 USANDO DEL SISTEMA                     | 0.2        |

|    | GENERADOR DE XILINX                                                                  | 82         |

|    | A.7.2.1 Procedimientos                                                               | 83         |

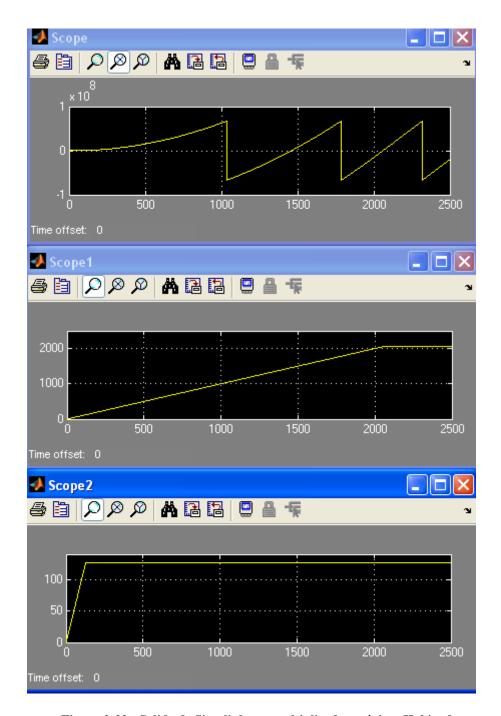

|    | A.7.2.2 Analizar la precisión y la muestra                                           | 88<br>94   |

|    | A.7.2.3 Conectar una Mac utilizando Xilink A.7.2.4 Configurar y simular el 12 x 8    | 94<br>97   |

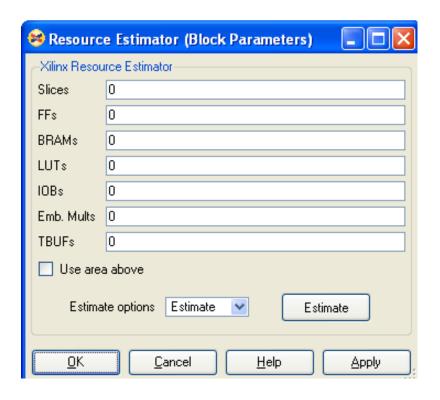

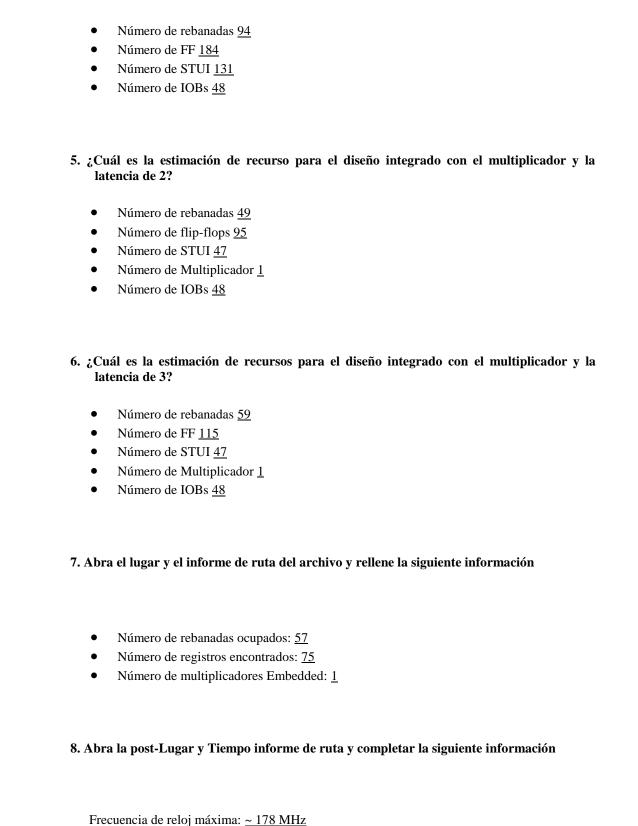

|    | A.7.2.5 Las estimaciones de recursos                                                 | 100        |

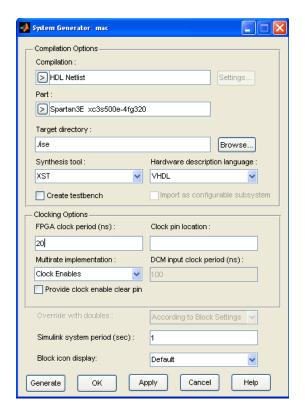

|    | A.7.2.6 Generar el paso HDL                                                          | 100        |

|    | A.7.2.7 Conclusiones                                                                 | 104        |

|    | A.7.3 PRACTICA TRES: ENRUTAMIENTO DE SEÑAL                                           | 106        |

|    | A.7.3.1 Procedimiento                                                                | 107        |

|    | A.7.3.2 Diseño de relleno lógico                                                     | 108        |

|    | A.7.3.3 Conclusión                                                                   | 110        |

|    | A.7.4 PRACTICA CUATRO: APLICACIÓN DE UN CONTROL                                      | 111        |

|    | A.7.4.1 Procedimiento                                                                | 112        |

|    | A.7.4.2 Desarrollando un modelo MCODE                                                | 113        |

|    | A.7.4.3 Conclusión                                                                   | 115        |

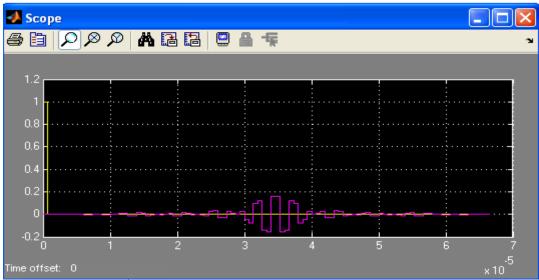

|    | A.7.5 PRACTICA CINCO: DISEÑO DE UNA FIR MAC                                          | 117        |

|    | A.7.5.1 Procedimiento                                                                | 121        |

|    | A.7.5.2 Añadir y parametrizar el paso de control logic 2                             | 122        |

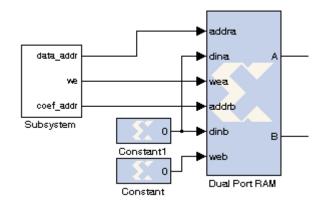

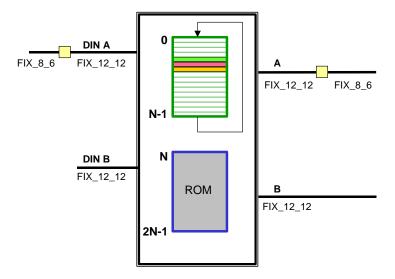

|    | A.7.5.3 Agregue el puerto doble de RAM                                               | 124        |

|    | A.7.5.4 Añadir relleno y un padding en el paso de los puertos                        | 127        |

|    | A.7.5.5 Completar el paso de diseño                                                  | 129        |

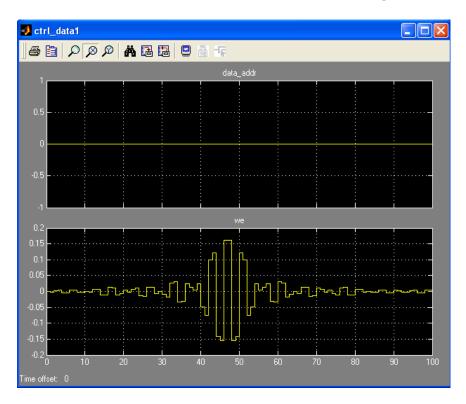

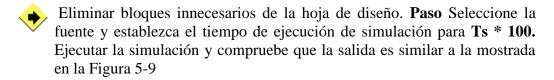

|    | A.7.5.6 Pruebas en el diseño con distintas fuentes de paso                           | 134        |

|    | A.7.5.7 Realización de hardware in the loop A.7.5.8 Conclusión                       | 137<br>140 |

|    | A.7.5.8 CONCIUSION A.7.6 PRACTICA SEIS: DISEÑO DE UN FILTRO FIR( RESPUESTA FINITA AL | 140        |

|    | IMPULSO)                                                                             | 141        |

|    | A.7.6.1 Procedimiento                                                                | 141        |

|    | A.7.6.2 Modelar y simular el filtro FIR                                              | 145        |

|    | A.7.6.3Realización de hardware in the loop                                           | 151        |

|    | A.7.6.4 Conclusión                                                                   | 154        |

|    |                                                                                      |            |

## ÍNDICE DE GRAFICOS

## CAPITULO 1

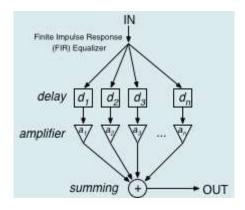

| Fig.1 Grafica del Filtro Digital                                               | 3  |

|--------------------------------------------------------------------------------|----|

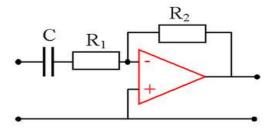

| Fig.2 Grafica de un Filtro Activo Paso Alto. Un amplificador operacional       | 7  |

| (elemento activo) resaltado en color rojo                                      |    |

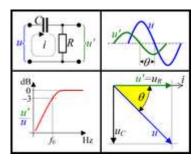

| Fig. 3 Grafica de un Filtro Pasivo Analógico de primer orden con circuito RC   | 9  |

| Fig. 4 Desfase entre señal de entrada y salida                                 | 10 |

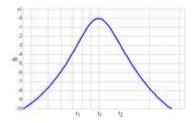

| Fig. 5 Grafica de la Respuesta frecuencial de un filtro pasa banda             | 11 |

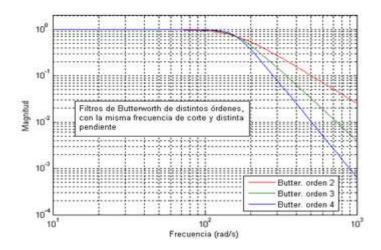

| Fig. 6 Grafica de Filtros de Butterworth de varios órdenes                     | 15 |

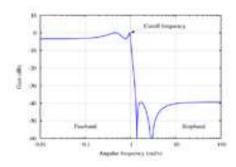

| Fig. 7 Grafica de la Respuesta de un filtro de Cauer                           | 17 |

| Fig. 8 Grafica de la Estructura del F. IIR                                     | 23 |

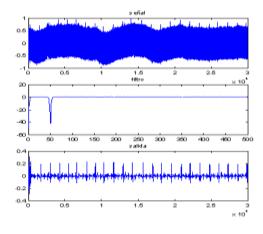

| Fig. 9 Grafica del aspecto del filtro en el centro. En la parte superior se    | 24 |

| muestra la señal que se quiere filtrar y en la parte inferior la señal         |    |

| filtrada                                                                       |    |

| Fig. 10 Grafica del Sistema basado en un DSP                                   | 27 |

|                                                                                |    |

| CAPITULO 2                                                                     |    |

| Fig. 1 Grafica de xilinx spartan 3                                             | 31 |

| Fig. 2 Grafica de los elementos de Xilinx de la FPGA                           | 32 |

| Fig. 3 Descripción de las distintas etapas en el flujo de diseño de un sistema | 41 |

| digital                                                                        |    |

| Fig. 4 ISE Project Window Navigator (clip de pantalla de Xilinx (TM) ISE)      | 43 |

| Fig. 5 Gráfica de un sistema de control usando Toolbox                         | 48 |

| CAPITULO 3                                                                     |    |

|                                                                                |    |

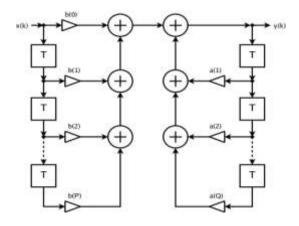

| Fig. 1 Grafica de la estructura del Filtro Fir                                 | 52 |

| Fig. 2 Gráfica de ruido blanco                                                 | 56 |

| Fig. 3 Kit de desarrollo XILINX SPARTAN 3E                                     | 58 |

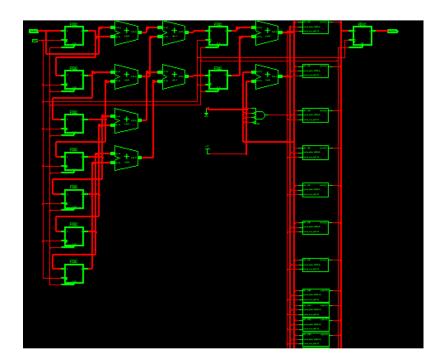

| Fig. 4 Entidad de un filtro Fir en FPGA XILINX                                 | 59 |

| Fig. 5 Esquema RTL                                                             | 60 |

## INTRODUCCIÓN

Es cada vez mayor el uso que la industria da a las FPGAs, un tipo particular de circuito integrado de gran versatilidad y de relativo bajo coste. Mientras que hace unos pocos años, el desarrollo de aplicaciones digitales integradas concretas requería el empleo, en muchos casos, de circuitos integrados de aplicación específica (ASIC), en la actualidad, el desarrollo alcanzado por las FPGAs ha permitido su empleo cada vez más intensivo.

En campos tan diversos como el procesamiento digital de la señal o el power line la FPGA está mostrando su versatilidad y el bajo coste asociado al desarrollo de aplicaciones en ellas. Mientras que un desarrollo de un ASIC requería grandes esfuerzos para la implementación correcta de aplicaciones, las FPGAs poseen librerías completas y gran facilidad para la programación de las mismas.

Debida a esa mayor importancia que adquiere en el mercado y la industria este tipo de integrado, nos ha parecido útil el mostrar una aplicación concreta de las mismas en la actualidad. Esta aplicación, el filtrado digital de la señal, nos muestra cómo ha evolucionado la tecnología para posibilitar estas nuevas aplicaciones.

También FPGAs Xilinx, ya que fue el primero en usar las tablas de búsqueda para construir lógica de usuario. Estas tablas de verdad lógicas son incrustadas en bloques lógicos configurables (configurable logic blocks o CLBs) que también incluyen una pareja de flips flops tipo D y circuitos para control y activación del reloj. La base literal del CLB es un SRAM (RAM estática) que almacena el patrón

de bits que define las funciones lógicas del CLB y los caminos ligados a ellos. Los patrones de bits SRAM son cargados de una forma variada de modos de configuración, y, como con cualquier RAM, puede ser recargado o escrito un número de veces ilimitado.

El diseño puede ser corregido o modificado a través de configuraciones programadas con ningún cambio en el hardware. Los datos de configuración pueden ser cargados desde un ordenador servidor o pueden ser transferidos desde una memoria PROM local de forma automática con el encendido del dispositivo.

Como estos productos FPGA ya están maduros, una librería de macros diseñados de forma óptima y probados han sido desarrollados para facilitar las tareas del diseñador.

De esa forma podemos encontrar contadores, registros de desplazamiento, sumadores paralelo y acumuladores, memorias RAM, FIFOs, etc, que pueden ser compiladas o escaladas a las dimensiones deseadas para satisfacer los requerimientos.

## **CAPITULO I**

## FILTRO DIGITAL

## 1.1.0 INTRODUCCIÓN AL DISEÑO DE FILTROS DIGITALES

Un filtro digital es un sistema que, dependiendo de las variaciones de las señales de entrada en el tiempo y amplitud (Fig. 1), se realiza un procesamiento matemático sobre dicha señal; generalmente mediante el uso de la Transformada rápida de Fourier; obteniéndose en la salida el resultado del procesamiento matemático o la señal de salida.

Fig.1 Grafica del Filtro Digital

Los filtros digitales tienen como entrada una señal analógica o digital y en su salida tienen otra señal analógica o digital, pudiendo haber cambiado en amplitud, frecuencia o fase dependiendo de las características del filtro digital.

El filtrado digital es parte del procesado de señal digital. Se le da la denominación de digital más por su funcionamiento interno que por su dependencia del tipo de señal a filtrar, así podríamos llamar filtro digital tanto a un filtro que realiza el procesado de señales digitales como a otro que lo haga de señales analógicas.

Comúnmente se usa para atenuar o amplificar algunas frecuencias, por ejemplo se puede implementar un sistema para controlar los tonos graves y agudos del audio del estéreo del auto.

La gran ventaja de los filtros digitales sobre los analógicos es que presentan una gran estabilidad de funcionamiento en el tiempo.

El filtrado digital consiste en la realización interna de un procesado de datos de entrada.

En general el proceso de filtrado consiste en el muestreo digital de la señal de entrada, el procesamiento considerando el valor actual de entrada y considerando las entradas anteriores.

El último paso es la reconstrucción de la señal de salida.

#### 1.2.0 MECANISMO DEL PROCESAMIENTO DEL FILTRO DIGITAL

## En general la mecánica del procesamiento es:

Tomar las muestras actuales y algunas muestras anteriores (que previamente habían sido almacenadas) para multiplicadas por unos coeficientes definidos.

También se podría tomar valores de la salida en instantes pasados y multiplicarlos por otros coeficientes.

Finalmente todos los resultados de todas estas multiplicaciones son sumados, dando una salida para el instante actual.

El procesamiento interno y la entrada del filtro serán digitales, por lo que puede ser necesario una conversión analógica-digital o digital-analógica para uso de filtros digitales con señales analógicas.

Un tema muy importante es considerar las limitaciones del filtro de entrada debido a Teorema de muestreo de Nyquist-Shannon que en pocas palabras; si quiero procesar hasta una frecuencia de 10KHz, debo muestrear a por lo menos 20 KHz. Los filtros digitales se usan frecuentemente para tratamiento digital de la imagen o para tratamiento del sonido digital. Otro ejemplo común de filtros digitales son los programas para retocar imágenes.

## 1.3.0 TIPOS DE FILTROS

Hay distintos tipos de clasificación de filtros.

## De acuerdo a la ganancia:

- Filtros pasivos

- > Filtros activos

## De acuerdo a su respuesta en frecuencia:

|   | -                    |

|---|----------------------|

| > | Filtro pasa bajo     |

| > | Filtro pasa alto     |

|   | Filtro pasa banda    |

| > | Filtro rechaza banda |

## De acuerdo al método de diseño:

- > Filtro de Butterworth

- > Filtro de Chebyshov I y Filtro de Chebyshov II

- Filtro de Cauer (elíptico)

- Filtro de Bessel

## De acuerdo a su aplicación:

Filtro de red.

## **Otros Filtros:**

- > Filtros piezoeléctricos.

- Filtro Analógicos

- Filtro Digital

- ➤ Filtro FIR

- > Filtro IIR

#### 1.3.1 De acuerdo a la ganancia:

#### Filtro Activo

Un filtro activo es un filtro electrónico analógico distinguido por el uso de uno o más componentes activos (que proporcionan una cierta forma de amplificación de energía), que lo diferencian de los filtros pasivos que solamente usan componentes pasivos. Típicamente este elemento activo puede ser un tubo de vacío, un transistor o un amplificador operacional.

**Fig. 2** Grafica de un Filtro Activo Paso Alto. Un amplificador operacional (elemento activo) resaltado en color rojo.

Un filtro activo puede presentar ganancia en toda o parte de la señal de salida respecto a la señal de entrada. En su implementación se combinan elementos activos y pasivos, siendo frecuente el uso de amplificadores operacionales, que permite obtener resonancia y un elevado factor Q sin el empleo de bobinas.

Se pueden implementar, entre otros, filtros pasa bajo, pasa alto, pasa banda. Configuraciones de circuitos de filtro activo incluyen:

- Filtro de Sallen-Key

- Filtro de estado variable

#### Filtro Pasivo

El filtro pasivo es un filtro electrónico formado únicamente por elementos pasivos, es decir, resistencias, condensadores y bobinas.

## 1.3.2 De De acuerdo a su respuesta en frecuencia:

## Filtro Pasa Bajo

Un filtro pasa bajo corresponde a un filtro caracterizado por permitir el paso de las frecuencias más bajas y atenuar las frecuencias más altas. El filtro requiere de dos terminales de entrada y dos de salida, de una caja negra, también denominada cuadripolo o bipuerto, así todas las frecuencias se pueden presentar a la entrada, pero a la salida solo estarán presentes las que permita pasar el filtro. De la teoría se obtiene que los filtros están caracterizados por sus funciones de transferencia, así cualquier configuración de elementos activos o pasivos que consigan cierta función de transferencia serán considerados un filtro de cierto tipo.

En particular la función de transferencia de un filtro pasa bajo de primer orden corresponde a  $H(s)=k\frac{1}{1+\frac{s}{\omega_c}}$ , donde la constante k es sólo una ponderación correspondiente a la ganancia del filtro, y la real importancia reside en la forma de la función de transferencia  $\frac{1}{1+\frac{s}{\omega_c}}$ , la cual determina el comportamiento del filtro. En la función de transferencia anterior  $\omega_c$  corresponde a la frecuencia de corte propia del filtro, es decir la frecuencia a partir de la cual el se empieza a atenuar la señal de entrada.

De forma análoga al caso de primer orden, los filtros de pasa bajo de mayor orden también se caracterízan por su función de transferencia, por ejemplo la de un filtro paso bajo de segundo orden corresponde a  $H(s) = K \frac{\omega_o^2}{s^2 + 2(\omega_o s + \omega_o^2)}$ , donde  $\omega_O$  es la frecuencia natural del filtro y  $\xi$ es el factor de amortiguamiento de este.

#### Filtro Pasa Alto

Un filtro pasa alto (HPF) es un tipo de filtro electrónico en cuya respuesta en frecuencia se atenúan las componentes de baja frecuencia pero no las de alta frecuencia, éstas incluso pueden amplificarse en los filtros activos. La alta o baja frecuencia es un término relativo que dependerá del diseño y de la aplicación.

Fig. 3 Grafica de un Filtro Pasivo Analógico de primer orden con circuito RC

## Implementación

Si se estudia este circuito (con componentes ideales) para frecuencias muy bajas, en continua por ejemplo, se tiene que el condensador se comporta como un circuito abierto, por lo que no dejará pasar la corriente a la resistencia, y su diferencia de tensión será cero. Para una frecuencia muy alta, idealmente infinita, el condensador se comportará como un cortocircuito, es decir, como si no

estuviera, por lo que la caída de tensión de la resistencia será la misma tensión de entrada, lo que significa que dejaría pasar toda la señal.

Por otra parte, el desfase entre la señal de entrada y la de salida si que varía, como puede verse en la Figura # 4.

Fig. 4: Desfase entre señal de entrada y salida.

El filtro pasa alto más simple es un circuito RC en serie en el cual la salida es la caída de tensión en la resistencia.

El producto de resistencia por condensador (R×C) es la constante de tiempo, cuyo recíproco es la frecuencia de corte, es decir, donde el módulo de la respuesta en frecuencia baja 3dB respecto a la zona pasante:  $\theta = \tan^{-1} \frac{f_c}{f}$

Donde fc es la frecuencia de corte en hercios, R es la resistencia del tweteer o parlante en ohmios y C es la capacidad en faradios. El desfase depende de la frecuencia f de la señal y sería:  $f_c = \frac{1}{2\pi RC}$

## **Aplicaciones**

Una posible aplicación de este tipo de filtro sería la de hacer que las altas frecuencias de una señal de audio fuesen a un altavoz para sonidos agudos mientras que un filtro pasa bajo haría lo propio con los graves.

Otra aplicación sería la de eliminar los ruidos que provienen de la red eléctrica (50 o 60Hz) en un circuito cuyas señales fueran más altas.

#### Filtro Pasa Banda

Un filtro pasa banda es un tipo de filtro electrónico que deja pasar un determinado rango de frecuencias de una señal y atenúa el paso del resto.

Fig.5 Grafica de la Respuesta frecuencial de un filtro pasa banda

## Implementación

Un circuito simple de este tipo de filtros es un circuito RLC (resistencia, bobina y condensador) en el que se deja pasar la frecuencia de resonancia, que sería la frecuencia central (fc) y las componentes frecuenciales próximas a ésta, en el diagrama hasta f1 y f2. No obstante, bastaría con una simple red resonante LC.

Otra forma de construir un filtro pasa banda puede ser usar un filtro pasa bajo en serie con un filtro pasa alto entre los que hay un rango de frecuencias que ambos dejan pasar. Para ello, es importante tener en cuenta que la frecuencia de corte del pasa bajo sea mayor que la del pasa alto, a fin de que la respuesta global sea pasa banda (esto es, que haya solapamiento entre ambas respuestas en frecuencia).

Un filtro ideal sería el que tiene unas bandas pasante y de corte totalmente planas y unas zonas de transición entre ambas nulas, pero en la práctica esto nunca se consigue, siendo normalmente más parecido al ideal cuando mayor sea el orden del filtro, para medir cuanto de "bueno" es un filtro se puede emplear el denominado factor Q. En filtros de órdenes altos suele aparecer un rizado en las zonas de transición conocido como efecto Gibbs.

Un filtro pasa banda más avanzado sería los de frecuencia móvil, en los que se pueden variar algunos parámetros frecuenciales, un ejemplo es el circuito anterior RLC en el que se sustituye el condensador por un diodo varicap o varactor, que actúa como condensador variable y, por lo tanto, puede variar su frecuencia central.

## **Aplicaciones**

Estos filtros tienen aplicación en ecualizadores de audio, haciendo que unas frecuencias se amplifiquen más que otras. Otra aplicación es la de eliminar ruidos que aparecen junto a una señal, siempre que la frecuencia de ésta sea fija o conocida.

Fuera de la electrónica y del procesado de señal, un ejemplo puede ser dentro del campo de las ciencias atmosféricas, donde son usados para manejar los datos dentro de un rango de 3 a 10 días.

De acuerdo con su orden:

- Primer orden

- Segundo orden

De acuerdo con el tipo de respuesta ante entrada unitaria:

- ➤ FIR (Finite Impulse Response)

- ➤ IIR (Infinite Impulse Response)

- ➤ TIIR (Truncated Infinite Impulse Response)

#### Filtro rechaza banda

El filtro suprime banda, filtro elimina banda, filtro notch, filtro trampa o filtro de rechazo de banda es un filtro electrónico que no permite el paso de señales cuyas frecuencias se encuentran comprendidas entre las frecuencias de corte superior e inferior.

Pueden implementarse de diversas formas. Una de ellas consistirá en dos filtros, uno paso bajo cuya frecuencia de corte sea la inferior del filtro elimina banda y otro paso alto cuya frecuencia de corte sea la superior del filtro elimina banda. Como ambos son sistemas lineales e invariantes, la respuesta en frecuencia de un filtro banda eliminada se puede obtener como la suma de la respuesta paso bajo y

la respuesta paso alto (hay que tener en cuenta que ambas respuestas no deben estar solapadas para que el filtro elimine la banda que interese suprimir), ello se implementará mediante un sumador analógico, hecho habitualmente con un amplificador operacional.

Otra forma más sencilla, si bien presenta una respuesta en frecuencia menos selectiva, sería la de colocar lo que se conoce como "circuito trampa". En efecto, si unimos las dos bornas (la considerada activo y la considerada masa) con un dipolo resonante LC serie o paralelo, la respuesta global sería la de un filtro elimina banda (el mínimo de la respuesta estaría en la frecuencia de resonancia del dipolo resonante). En este enlace se puede encontrar un ejemplo de filtro elimina banda (realmente se muestran los cuatro tipos de filtros, el filtro notch es el último de todos ellos) construido únicamente con componentes pasivos.

#### 1.3.3 Atendiendo el método del diseño:

#### Filtro de Butterworth

El filtro de Butterworth más básico es el típico filtro paso bajo de primer orden, el cual puede ser modificado a un filtro pasa alto o añadir en serie otros formando un filtro pasa banda o elimina banda y filtros de mayores órdenes.

Fig. 6 Grafica de Filtros de Butterworth de varios órdenes

Según lo mencionado antes, la respuesta en frecuencia del filtro es máximamente plana (con las mínimas ondulaciones) en la banda pasante. Visto en un diagrama de Bode con escala logarítmica, la respuesta decae linealmente desde la frecuencia de corte hacia menos infinito. Para un filtro de primer orden son -20 dB por década (aprox. -6dB por octava).

El filtro de Butterworth es el único filtro que mantiene su forma para órdenes mayores (sólo con una caída de más pendiente a partir de la frecuencia de corte).

Este tipo de filtros necesita un mayor orden para los mismos requerimientos en comparación con otros, como los de Chebyshev o el elíptico.

## Diseño

Si llamamos H a la respuesta en frecuencia, se debe cumplir que las 2N-1 primeras derivadas  $|H(\Omega)|^2$  de sean cero para  $\Omega=0$  y  $\Omega=\infty$ . Únicamente posee polos y la función de transferencia es:  $|H(\Omega)|^2 - \frac{1}{1+(\Omega/\Omega)^{1/2}}$

donde N es el orden del filtro,  $\Omega$ c es la frecuencia de corte (en la que la respuesta cae 3 dB por debajo de la banda pasante) y  $\Omega$  es la frecuencia analógica compleja ( $\Omega$ =j w).

El diseño es independiente de la implementación, que puede ser por ejemplo mediante células de Sallen-Key o Rauch, componentes discretos, etc.

## Filtro de Chebyshev

En los filtros de Chebyshev lo que ocurre es que consiguen una caída de la respuesta en frecuencia más pronunciada en frecuencias bajas debido a que permiten más rizado que otros filtros en alguna de sus bandas. Se conocen dos tipos de filtros de Chebyshev los cuales son:

## Filtro de Chebyshev de tipo I

Son filtros que únicamente tienen polos, presentan un rizado constante en la banda pasante y presentan una caída monótona en la banda no pasante. La respuesta en frecuencia  $|H(\Omega)|^2 - \frac{1}{1+\epsilon^2T_N^2\left(\frac{\Omega}{\Omega_*}\right)}$  es: para  $0 \le \epsilon \le 1$

donde N es el orden del filtro,  $\Omega$ c es la frecuencia de corte,  $\Omega$  es la frecuencia analógica compleja ( $\Omega$ =j w) y TN(x) es el polinomio de Chebyshov de orden N, que se define  $T_{N+1}=2\cdot x\cdot T_N(x)-T_{N-1}(x)$  como: con  $T_0(x)=1$  y  $T_1(x)=x$

En estos filtros la frecuencia de corte no depende de N y el módulo de su respuesta en frecuencia oscila (rizado) entre 1 y  $\frac{1}{\sqrt{1+\epsilon^2}}$ .

## Filtro de Chebyshev de tipo II

Estos filtros a diferencia de los Chebyshev I presentan ceros y polos, su rizado es constante en la banda no pasante y además presentan una caída monotónica en la banda pasante. Su respuesta en frecuencia  $|H(\Omega)|^2 = \frac{1}{1+\epsilon^2 + \frac{T_N^2(\Omega_n/\Omega_0)}{T_N^2(\Omega_n/\Omega)}}$  es: para  $0 \le \epsilon \le 1$ . En un diagrama de circunferencia unidad, los polos estarían en una elipse y los ceros sobre el eje imaginario.

#### Filtro de Cauer

Un filtro elíptico o filtro de Cauer es un tipo de filtro eléctrico.

Están diseñados de manera que consiguen estrechar la zona de transición entre bandas y, además, acotando el rizado en esas bandas. La diferencia con el filtro de Chevyshev es que este sólo lo hace en una de las bandas.

Fig.7 Grafica de la Respuesta de un filtro de Cauer.

Estos filtros suelen ser más eficientes debido a que al minimizar la zona de transición, ante unas mismas restricciones consiguen un menor orden. Por el contrario son los que presentan una fase menos lineal.

#### Diseño

La respuesta en frecuencia de un filtro pasa bajo elíptico es:  $|H(\Omega)|^2 = \frac{1}{1+c^2 \cdot R_N(\Omega/\Omega_c)}, \text{ para } 0 \le \epsilon \le 1, \text{ donde N es el orden del filtro, } \Omega \text{c es la}$  frecuencia de corte,  $\Omega$  es la frecuencia analógica compleja ( $\Omega$ =j w) y RN (x) es la función jacobiana elíptica de orden N, normalmente de primera clase:  $R_N(x) = \int_0^{2\pi} \frac{1}{\sqrt{1-x^2 \cdot \sin^2\theta}} d\theta$

#### Filtro de Bessel

Son filtros que únicamente tienen polos. Están diseñados para tener una fase lineal en las bandas pasantes, por lo que no distorsionan las señales; por el contrario tienen una mayor zona de transición entre las bandas pasantes y no pasantes.

Cuando estos filtros se transforman a digital pierden su propiedad de fase lineal. Su respuesta en frecuencia es:  $H(s) = \frac{1}{\sum_{k=0}^{N} a_k \cdot s^k}$ , donde N es el orden del filtro y el denominador es un polinomio de Bessel, cuyos coeficientes son:  $a_k = \frac{(2N-k)!}{2^{N-k} \cdot k! \cdot (N-k)!}$ , con k = 0, 1, 2, ..., N.

## 1.3.4 De acuerdo a su aplicación:

#### Filtro de red

Este tipo de circuito impide la entrada de ruido externo, además impide que el sistema contamine la red, de tal forma que se pueden utilizar fuentes analógicas y digitales o fuentes PWM que afecten negativamente el resto del equipo. También es posible corregir el factor de potencia ya que el circuito reduce significativamente los picos de corriente generados por el condensador al cargarse. El circuito consiste básicamente en un filtro paso bajo en donde la primera bobina elimina ruido en general (frecuencias altas), junto con los condensadores. El transformador elimina el ruido sobrante, que los condensadores no eliminan. Al transformador se le denomina choque de modo común. Son los utilizados para garantizar la calidad de la señal de alimentación, éstos tienen como objetivo eliminar ruidos tanto en modo común como en modo diferencial.

## 1.3.5 Otros tipos:

## Filtros Piezoeléctricos

Este filtro aprovecha las propiedades resonantes de determinados materiales como el cuarzo. Este cristal de cuarzo se utiliza como componente de control de la frecuencia de circuitos osciladores convirtiendo las vibraciones mecánicas en voltajes eléctricos a una frecuencia específica. Esto ocurre debido al efecto piezoeléctrico. En un material piezoeléctrico, al aplicar una presión mecánica sobre

un eje, dará como consecuencia la creación de una carga eléctrica. En algunos materiales, se encuentra que aplicando un campo eléctrico según un eje, produce una deformación mecánica según otro eje ubicado a un ángulo recto respecto al primero. Por las propiedades mecánicas, eléctricas, y químicas, el cuarzo es el material más apropiado para fabricar dispositivos con frecuencia bien controlada. También existen filtros como el de ferrita que existe en muchos cables. Es normal encontrárselos en las pantallas del computador. Aquí se tiene la propiedad de presentar distintas impedancias a alta y baja frecuencia.

## Filtro Analógico

Cualquier filtro, tiene una entrada y una salida, así que si hablamos de un filtro pasabajo, lo podemos ver, como una caja negra con dos terminales de entrada y dos de salida. Si un terminal de entrada es común a la salida tendremos un sistema desbalanceado (Unbalance, en inglés), así las cosas, si llamamos e1 y e2 a los terminales de entrada y s1 y s2 a los de salida, un filtro pasabajo sencillo, sería, colocar una resistencia entre e1 y s1 y un condensador, entre s1 y s2, uniendo e2 con s2, tenemos un filtro pasa bajo desbalanceado. Ahora veamos como trabaja: las diferentes frecuencias ingresan por e1-e2 y salen por s1-s2, las altas frecuencias verán en el condensador una baja impedancia (cortocircuito) mientras que las bajas frecuencias seguirán de largo por las salidas s1-s2 hacia el circuito siguiente, cumpliendo con la función de dejar pasar las bajas frecuencias y atenuar las altas. Esto a grandes rasgos. También como se describe abajo, se puede usar una bobina, entre e1 y s1 y los terminales e2 y s2 se unen, teniendo así un filtro

pasa bajo desbalanceado, el cual se rige por XL=WL, donde XL es la reactancia inductiva y w la frecuencia angular y L la inductancia, como se ve abajo del escrito.

El más sencillo está armado en una resistencia y un condensador (o bobina). Pero podría ser mejor. Un filtro analógico elemental compuesto por un capacitor se denomina, "Filtro pasa altos" (debido a que la Reactancia Capacitiva Xc = 1/WC). Mientras que el compuesto por una inductancia (bobina, o choque) es un "filtro pasa bajos" (debido a que la Reactancia Inductiva Xl = WL).

## Filtro Digital

La ecuación de un filtro paso bajo digital de primer orden es:  $y[n] = y[n-1] + \frac{x[n] - y[n-1]}{A}$ , Donde A ha de ser mayor que uno. También es llamado filtro promediador, debido a que promedia las muestras de la entrada y por lo tanto suprime variaciones rápidas, característica que le otorga el carácter de paso bajo. Su transformada Z es:  $H(Z) = \frac{1}{A}(1+Z^{-1})$

#### Ancho De Banda

Un filtro pasa bandas ideal posee dos espectros uno ubicado en wo y otro en -wo, siendo wo la frecuencia central del filtro, si el mismo posee un ancho de banda b los espectros seria: -wo - b/2 y -wo + b/2; wo - b/2 y wo + b/2.

#### Filtro IIR

IIR es una sigla en inglés para Infinite Impulse Response o Respuesta infinita al impulso. Se trata de un tipo de filtros digitales en el que, como su nombre indica, si la entrada es una señal impulso, la salida tendrá un número infinito de términos no nulos, es decir, nunca vuelve al reposo.

## Expresión matemática de los filtros IIR

La salida de los filtros IIR depende de las entradas actuales y pasadas, y además de las salidas en instantes anteriores. Esto se consigue mediante el uso de realimentación de la salida.  $y_n = b_0 x_n + b_1 x_{n-1} + \dots + b_N x_{n-N} - a_1 y_{n-1} - a_2 y_{n-2} - \dots - a_M y_{n-M}$ .

Donde los a y b son los coeficientes del filtro. El orden es el máximo entre los valores de M y N. Aplicando la transformada Z a la expresión anterior:

$$H(z) = \frac{\sum_{k=0}^{M} b_k z^{-k}}{1 - \sum_{k=1}^{N} a_k z^{-k}}$$

#### Estructura

Hay numerosas formas de implementar los filtros IIR. La estructura afecta a las características finales que presentará el filtro como la estabilidad. Otros parámetros a tener en cuenta a la hora de elegir una estructura es el gasto computacional que presenta.

Fig. 8 Grafica de la Estructura del F. IIR

## Polos y ceros

Este tipo de filtros presenta polos y ceros que determinan la estabilidad y la causalidad del sistema. Cuando todos los ceros están en el interior de la circunferencia unidad se dice que es fase mínima. Si todos están en el exterior es fase máxima. Si algún polo está fuera de la circunferencia unidad el sistema es inestable.

## Diseño de filtros IIR

Las formas habituales de diseñar este tipo de filtros son:

- Indirecta (a partir de prototipos analógicos)

- > Impulso invariante

- Aproximación de derivadas

- > Transformación bilineal

- Directa

- Aproximación de Padé

- Aproximación de mínimos cuadrados

## Ejemplo del diseño de un filtro

En primer lugar se parte de las especificaciones y, basándose en éstas, se elige el tipo de filtro. En este ejemplo se parte de un filtro digital que anule las frecuencias menores a 5Hz y la de 50Hz y que no altere al resto, la frecuencia de muestreo será 1000Hz, además se quiere fase lineal. Con estas especificaciones se elige un filtro FIR. El diseño se puede hacer manualmente o con la ayuda de un ordenador. En este ejemplo el método de diseño será el de Remez. En Matlab se obtienen los coeficientes que definen el filtro, que en la ecuación anterior se llaman a y b (el numerador es la variable b y el denominador solo tiene un término que es 1, como corresponde a un filtro FIR):[n, fo ,mo ,w]=remezord ([0 5 45 50 50 55], [0 1 0 1], [0.01 0.1 0.01 0.1], 1000); b = remez(n, fo, mo, w, w).

**Fig. 9** Grafica del aspecto del filtro en el centro. En la parte superior se muestra la señal que se quiere filtrar y en la parte inferior la señal filtrada (se trata de un electrocardiograma).

El siguiente paso es seleccionar la forma de implementarlo, es decir su estructura.

Luego se elige el hardware sobre el que funcionará. Normalmente un Procesador

digital de señal o una FPGA, aunque también puede ser un programa de

ordenador. Finalmente se usan los coeficientes obtenidos y la estructura elegida

para crear el programa.

Características

Las principales diferencias respecto a los filtros FIR es que los IIR pueden

cumplir las mismas exigencias que los anteriores pero con menos orden de filtro.

Esto es importante a la hora de implementar el filtro, pues presenta una menor

carga computacional.

Este tipo de filtros puede ser inestable, aún cuando se diseñen para ser estables.

En principio no pueden diseñarse para tener fase lineal pero se pueden aplicar

algunas técnicas como el filtrado bidireccional para lograrlo.

De acuerdo con la estructura con que se implementa:

Laticce

Varios en cascada

Varios en paralelo

25

## Expresión general de un filtro

Hay muchas formas de representar un filtro. Por ejemplo, en función de w (frecuencia digital), en función de z y en función de n (número de muestra). Todas son equivalentes, pero a la hora de trabajar a veces conviene más una u otra. Como regla general se suele dejar el término a0=1.

Si se expresa en función de z y en forma de fracción:  $H(z) = \frac{\sum_{k=0}^{M} b_k \cdot z^{-k}}{\sum_{k=0}^{N} a_k \cdot z^{-k}}. Y \text{ en}$  dominio de n:  $y(n) = \sum_{k=0}^{N} b_k \cdot x(n-k) = \sum_{k=1}^{M} a_k \cdot y(n-k)$

Los coeficientes son los a y b y son los que definen el filtro, por lo tanto el diseño consiste en calcularlos.

## 1.4.0 IMPORTANCIA EN PROCESAMIENTO DIGITAL DE SEÑALES

## 1.4.1 Que es DSP?

DSP es el acrónimo de *Digital Signal Processor*, que significa Procesador Digital de Señal. Un DSP es un sistema basado en un procesador o microprocesador que posee un juego de instrucciones, un hardware y un software optimizados para aplicaciones que requieran operaciones numéricas a muy alta velocidad. Debido a esto es especialmente útil para el procesado y representación de señales analógicas en tiempo real: en un sistema que trabaje de esta forma (tiempo real) se reciben muestras (samples en inglés), normalmente provenientes de un conversor

analógico/digital (ADC). Se ha dicho que puede trabajar con señales analógicas, pero es un sistema digital, por lo tanto necesitará un conversor analógico/digital a su entrada y digital/analógico en la salida. Como todo sistema basado en procesador programable necesita una memoria donde almacenar los datos con los que trabajará y el programa que ejecuta. Si se tiene en cuenta que un DSP puede trabajar con varios datos en paralelo y un diseño e instrucciones específicas para el procesado digital, se puede dar una idea de su enorme potencia para este tipo de aplicaciones. Estas características constituyen la principal diferencia de un DSP y otros tipos de procesadores. Para adentrar en su funcionamiento se pondrá el ejemplo de un filtro: el DSP recibirá valores digitales o samples procedentes de la señal de entrada, calcula qué salida se obtendrá para esos valores con el filtro que se le ha programado y saca esa salida.

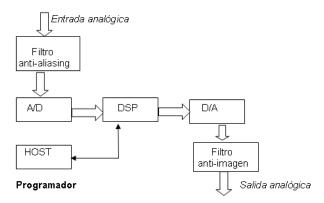

Fig. 10 Grafica del Sistema basado en un DSP

La señal entrante entra directamente en un filtro antialiasing para evitar frecuencias superiores a la de muestreo del conversor analógico-digital. Después se lleva a cabo el procesado digital en el módulo DSP, para después volverse a convertir en analógico y dar paso a la salida.

### 1.4.2 Aplicaciones

- Procesamiento digital de sonido

- Procesamiento digital de voz

- Procesamiento digital de imágenes

- Procesamiento digital de vídeo

Las aplicaciones más habituales en las que se emplean **DSP** son el procesado de audio y video; y cualquier otra aplicación que requiera el procesado en tiempo real. Con estas aplicaciones se puede eliminar el eco en las líneas de comunicaciones, lograr hacer más claras imágenes de órganos internos en los equipos de diagnóstico médico, cifrar conversaciones en teléfonos celulares para mantener privacidad, analizar datos sísmicos para encontrar nuevas reservas de petróleo, hace posible las comunicaciones wireless LAN, el reconocimiento de voz, los reproductores digitales de audio, los modems inalámbricos, las cámaras digitales, y una larga lista de elementos que pueden ser relacionados con el proceso de señales.

### 1.4.3 Importancia de las transformadas en el DSP

Uno de los beneficios principales del DSP es que las transformaciones de señales son más sencillas de realizar. Una de las más importantes transformadas es la Transformada de Fourier discreta (TFD). Esta transformada convierte la señal del dominio del tiempo al dominio de la frecuencia. La TDF permite un análisis más sencillo y eficaz sobre la frecuencia, sobre todo en aplicaciones de eliminación de

ruido y en otros tipos de filtrado (pasa bajos, filtros pasa altos, filtros pasa banda, filtros de rechazo de banda, etc.).

Otra de las transformadas importantes es la Transformada de Coseno Discreta la cual es similar a la anterior en cuanto a los cálculos requeridos para obtenerla, pero esta convierte a la señales en componentes del coseno trigonométrico. Esta transformada es una de las bases del algoritmo de compresión de imágenes JPEG.

### 1.4.4 Arquitectura

Un DSP está diseñado teniendo en cuenta las tareas más habituales del procesado digital: sumas, multiplicaciones y retrasos (almacenar en memoria).

Los DSP abandonan la arquitectura clásica de Von Neumann, en la que datos y programas están en la misma zona de memoria, y apuestan por la denominada Arquitectura Harvard. En una arquitectura Hardvard existen bloques de memoria físicamente separados para datos y programas. Cada uno de estos bloques de memoria se direcciona mediante buses separados (tanto de direcciones como de datos), e incluso es posible que la memoria de datos tenga distinta anchura de palabra que la memoria de programa (como ocurre en ciertos microcontroladores).

Los elementos básicos que componen un **DSP** son:

- Conversores en las entradas y salidas

- Memoria de datos, memoria de programa y DMA.

- MACs: multiplicadores y acumuladores.

ALU: Unidad aritmético-lógica.

Registros.

> PLL: Bucles enganchados en fase.

> PWM: Módulos de control de ancho de pulso.

1.4.5 Arquitecturas estándar en DSP

Las arquitecturas de los computadores actuales están comúnmente clasificadas

como RISC's (Reduced Instruction Set Computers) Conjunto de instrucciones de

reducción de equipos y CISC's (Complex Instruction Set Computers) Complejo de

instrucciones para equipos.

Estos últimos tienen un gran número de instrucciones sumamente poderosas,

mientras que la arquitectura RISC posee pocas instrucciones y realiza

movimientos de datos entre registros en un ciclo de máquina. Hoy en día los

computadores RISC comienzan a reemplazar a los CISC's, porque se puede

alcanzar un más alto rendimiento por medio del uso de un eficiente compilador

como a través de la ejecución de instrucciones simples en forma ordenada.

DSP's estándars tienen mucho rasgos de una arquitectura tipo RISC, aunque son

procesadores de propósitos específicos cuya arquitectura está especialmente

diseñada para operar en ambientes de alta necesidad de cálculo. Un DSP estándar

ejecuta varias operaciones en paralelo mientras que un RISC usa unidades

funcionales altamente eficientes que pueden iniciar y completar una instrucción

simple en uno o dos ciclos de reloj.

30

## **CAPITULO II**

### HERRAMIENTAS PARA EL FPGA Y SU ENTORNO DE DESARROLLO

Una FPGA (del inglés Field Programmable Gate Array) compuertas de arreglo o matrices programables, es un dispositivo semiconductor que contiene bloques de lógica cuya interconexión y funcionalidad se puede programar. La lógica programable puede reproducir desde funciones tan sencillas como las llevadas a cabo por una puerta lógica o un sistema combinacional hasta complejos sistemas en un chip (System-on-a-chip).

Fig.1 Grafica de xilinx spartan 3E

Las FPGAs se utilizan en aplicaciones similares a los ASICs sin embargo son más lentas, tienen un mayor consumo de potencia y no pueden abarcar sistemas tan complejos como ellos. A pesar de esto, las FPGAs tienen las ventajas de ser reprogramables (lo que añade una enorme flexibilidad al flujo de diseño), sus costes de desarrollo y adquisición son mucho menores para pequeñas cantidades de dispositivos y el tiempo de desarrollo es también menor.

Ciertos fabricantes cuentan con FPGAs que sólo se pueden programar una vez, por lo que sus ventajas e inconvenientes se encuentran a medio camino entre los ASICs y las FPGAs reprogramables.

Históricamente las FPGA surgen como una evolución de los conceptos desarrollados en las PLA (programable logic array) Red lógica programable y los CPLD(Complex Programmable Logic Device) Complejo de Dispositivos Lógicos Programables.

### 2.1.0 ELEMENTOS QUE CONFORMAN LOS FPGAS DE XILIX.

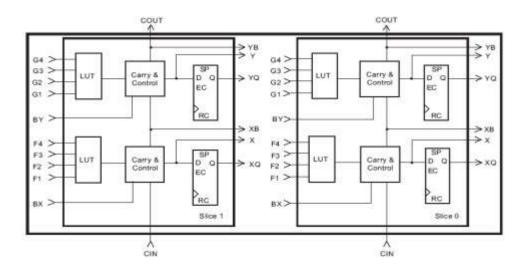

Elementos reconfigurables: CLBs e IOBs. Elemento básico del CLB es la celda lógica. Cada CLB puede tener varias de estas celdas lógicas (CL). Los CLB de Virtex tienen cuatro CL distribuidas en dos slices.

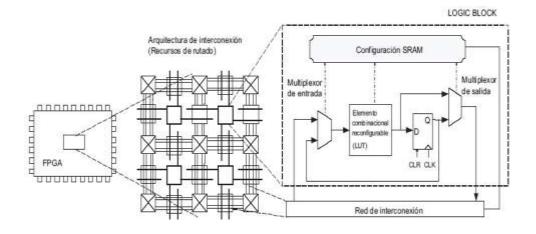

Fig. 2. Grafica de los elementos de xilinx de la FPGA.

### A. Contenido de la celda lógica.

La celda lógica de una FPGA de Xilinx contiene:

Generador de funciones (circuito programable LUT): Puede funcionar como circuito combinacional de 4 entradas o como memoria RAM 16x1.

Las memorias pueden ser de varios tamaño combinando varias LUTs.

También puede funcionar como registro de corrimiento de 16 bits.

### 2. Lógica de acarreo.

- 3. Elemento de memoria (para almacenar el resultado de la LUT). Matriz de ruteo global. Rutas horizontales y verticales con switches situados en la intersección entre las rutas. Para interconectar diferentes CLBs internamente.

- **B.** IOBs: Para interconectar los pines del FPGA y los CLBs.

- C. Rutas locales: Para interconectar CLBs localmente y para conectar los CLBs con la matriz de ruteo global.

- **D. Dispositivos para la gestión del reloj:** DDL en Spartan y DCMS en Virtex.

- **E. Memoria RAM:** No emplean recurso del CLB. Los bloques de memoria se distribuyen en las columnas cubriendo toda la altura del dispositivo.

También hay recursos de ruteo para conectar estos bloques con los CLBs. El contenido se fija mediante la memoria SRAM de configuración incluyéndose en el bitstream inicial o bitstream parciales posteriores. Estos bloques pueden funcionar como memoria ROM.

**F. Buffers de 3 estados:** Para conectar los CLBs a las rutas horizontales globales. Se llaman Tbufs.

Todos estos elementos se configuran mediante valores almacenados en celdas de memoria SRAM. Cambiar la funcionalidad del dispositivo equivales a cambiar los valores de esta memoria.

### 2.2.0 CARACTERÍSTICAS DE LAS FPGA

Una jerarquía de interconexiones programables permite a los bloques lógicos de un FPGA ser interconectados según la necesidad del diseñador del sistema, algo parecido a un breadboard(es una placa de uso genérico reutilizable o semi permanente) programable. Estos bloques lógicos e interconexiones pueden ser

programados después del proceso de manufactura por el usuario/diseñador, así que el FPGA puede desempeñar cualquier función lógica necesaria.

Una tendencia reciente ha sido combinar los bloques lógicos e interconexiones de los FPGA con microprocesadores y periféricos relacionados para formar un «Sistema programable en un chip».

Ejemplo de tales tecnologías híbridas pueden ser encontradas en los dispositivos Virtex-II PRO y Virtex-6 de Xilinx, los cuales incluyen uno o más procesadores PowerPC embebidos junto con la lógica del FPGA.

Muchos FPGA modernos soportan la reconfiguración parcial del sistema, permitiendo que una parte del diseño sea reprogramada, mientras las demás partes siguen funcionando.

Este es el principio de la idea de la «computación reconfigurable», o los «sistemas reconfigurables».

### 2.3.0 PROGRAMACIÓN FPGA

La tarea del programador es definir la función lógica que realizará cada uno de los CLB, seleccionar el modo de trabajo de cada IOB e interconectarlos.

El diseñador cuenta con la ayuda de entornos de desarrollo especializados en el diseño de sistemas a implementarse en un FPGA. Un diseño puede ser capturado ya sea como esquemático, o haciendo uso de un lenguaje de programación

especial. Estos lenguajes de programación especiales son conocidos como HDL o

Hardware Description Language (lenguajes de descripción de hardware). Los

HDLs más utilizados son:

VHDL : Lenguaje para descripción y modelado de circuitos

Verilog: Es un lenguaje de descripción de hardware

ABEL: designación de bases

En un intento de reducir la complejidad y el tiempo de desarrollo en fases de

prototipaje rápido, y para validar un diseño en HDL, existen varias propuestas y

niveles de abstracción del diseño. Entre otras, National Instruments LabVIEW

FPGA propone un acercamiento de programación gráfica de alto nivel.

TECNOLOGÍA DE LA MEMORIA DE PROGRAMACIÓN

En general existen 3 grandes tipos de dispositivos electrónicos: de memoria,

procesadores y de lógica.

Los dispositivos de memoria almacenan información aleatoria (archivos, hojas de

cálculo...)

Los procesadores ejecutan instrucciones de software para ejecutar una gran

variedad de tareas (ejecutar un programa de proceso de datos o un videojuego)

36

Los dispositivos de lógica proveen funciones específicas (comunicación entre dispositivos y el resto de funciones que un sistema debe ejecutar). A su vez, existen 2 tipos de categorías de dispositivos lógicos: los fijos y los programables. Xilinx esta en el negocio de los dispositivos de lógica programable.

Las FPGAs también se pueden diferenciar por utilizar diferentes tecnologías de memoria:

Volátiles: Basadas en RAM. Su programación se pierde al quitar la alimentación. Requieren una memoria externa no volátil para configurarlas al arrancar (antes o durante el reset).

No Volátiles: Basadas en ROM. Hay de dos tipos, las reprogramables y las no reprogramables.

**Reprogramables:** Basadas en EPROM o flash. Éstas se pueden borrar y volver a reprogramar aunque con un límite de unos 10.000 ciclos.

**No Reprogramables:** Basadas en fusibles. Solo se pueden programar una vez, lo que las hace poco recomendables para trabajos en laboratorios.

# 2.5.0 FORMAS DE ALMACENAR LOS VALORES (BITSTREAM) EN LA MEMORIA.

**Configuración serie:** El bitstream se lee desde una memoria PROM serie exterior.

### **Dos variantes:**

- Serie Maestro (Master): El FPGA genera el reloj de la carga.

- **Serie Esclavo** (**Slave**): El reloj lo genera otro dispositivo externo. Permite que la carga se realice desde un microprocesador externo.

**Configuración en paralelo:** Configuración a través de un puerto paralelo de 8 bits

• SelectMap (seleccionar mapa). La memoria de configuración esta dividida en frames.

A través del **SelectMap** se introducen frames concatenados en el bitstream. Aunque es un puerto de 8 bits, la configuración se realiza mediante paquetes de 32 bits.

El **SelectMap** dispone de varios registros internos. Registro de comandos, registro de control y registro de dirección. Los paquetes de configuración de 32 bits pueden incluir información para estos registros de forma que se controlan operaciones de lectura de la memoria de configuración o la reconfiguración parcial dinámica.

Configuración escaneo de límites (Boundary scan) (JTAG): La configuración se realiza mediante el protocolo serie JTAG.

La configuración es a través de la interfaz Boundary scan, que esta activa y accesible en todo momento. Es el sistema utilizado en la fase de desarrollo y depuración.

### 2.6.0 FABRICANTES DE DISPOSITIVOS FPGA

A principios de 2007, el mercado de los FPGA se ha colocado en un estado donde hay dos productores de FPGA de propósito general que están a la cabeza del mismo, y un conjunto de otros competidores quienes se diferencian por ofrecer dispositivos de capacidades únicas.

Xilinx es uno de los dos grandes líderes en la fabricación de FPGA.

Altera es el otro gran líder. Lattice Semiconductor lanzó al mercado dispositivos FPGA con tecnología de 90nm. En adición, Lattice es un proveedor líder en tecnología no volátil, FPGA basadas en tecnología Flash, con productos de 90nm y 130nm.

Actel tiene FPGAs basados en tecnología Flash reprogramable. También ofrece FPGAs que incluyen mezcladores de señales basados en Flash.

QuickLogic (lógica rápida) tiene productos basados en antifusibles (programables una sola vez).

Atmel es uno de los fabricantes cuyos productos son reconfigurables (el Xilinx XC62xx fue uno de estos, pero no están siendo fabricados actualmente). Ellos se enfocaron en proveer microcontroladores AVR con FPGAs, todo en el mismo encapsulado.

Achronix Semiconductor tienen en desarrollo FPGAs muy veloces. Planean sacar al mercado a comienzos de 2007 FPGAs con velocidades cercanas a los 2GHz.

MathStar, Inc. ofrecen FPGA que ellos llaman FPOA (Arreglo de objetos de matriz programable).

# 2.7.0 EL ENTORNO DE PROGRAMACION ISE DESIGN SUITE DE XILINX

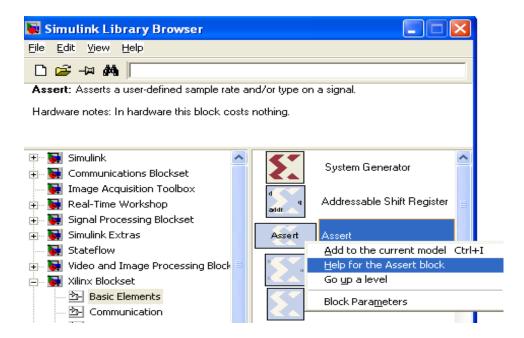

El sistema de Xilinx ISE es un entorno de diseño integrado que consiste en que un conjunto de programas para crear, simular e implementar diseños digitales en una FPGA o CPLD.

Todas las herramientas de uso de una interfaz gráfica de usuario (GUI) permiten a todos los programas ser ejecutados en las barras de herramientas, menús o iconos.

Esta escritura se destina a empezar con las herramientas de ISE. Da una visión rápida de cómo crear un diseño, simulación y descargar en una FPGA

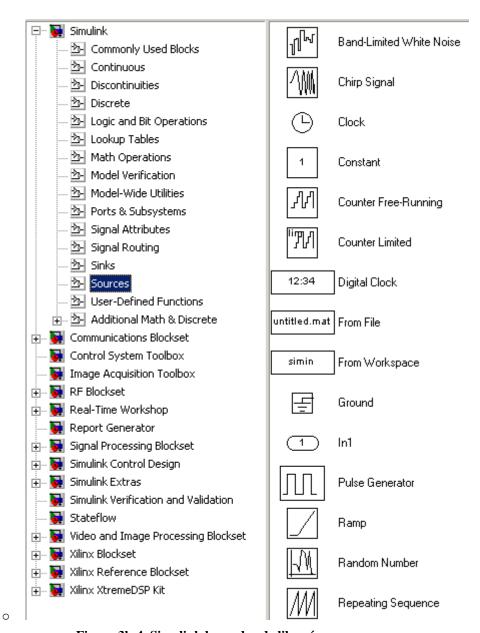

### 2.8.0 DISEÑO DE FLUJO GENERAL

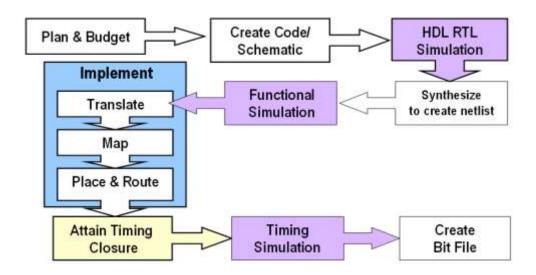

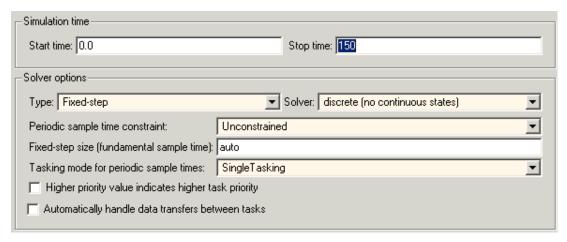

Los siguientes pasos están involucrados en la realización de un sistema digital usando Xilinx FPGAs, como lo ilustra la siguiente figura:

Fig.3 Descripción de las distintas etapas en el flujo de diseño de un sistema digital

### 2.8.1 Diseño de entrada

El primer paso es entrar a nuestro diseño. Esto puede hacerse mediante la creación de "Fuente" archivos. Los archivos de origen se pueden crear en diferentes formatos, tales como un esquema, o un lenguaje de descripción de hardware (HDL), tales como VHDL, Verilog o Abel. Un diseño del proyecto consistirá en un alto nivel de archivo de origen y de baja varios archivos de origen de nivel. Cualquiera de estos archivos puede ser un esquema o un archivo de HDL.

### 2.8.2 La síntesis

La etapa de síntesis crea los archivos de netlist de los archivos de origen diferentes. Los archivos de netlist pueden servir como entrada al módulo de aplicación.

### 2.8.3 Verificación

Este es un paso importante que debe hacerse en las distintas etapas del diseño. El simulador se utiliza para verificar la funcionalidad de un diseño (simulación funcional), el comportamiento y el tiempo (simulación de tiempo) de su circuito. Tiempo de simulación se ejecuta después de la aplicación de su circuito en la FPGA, ya que necesita conocer la ubicación real y de enrutamiento para determinar la velocidad exacta y el calendario del circuito.

### 2.8.4 Implementación

Después de generar el archivo de netlist (etapa de síntesis), la aplicación convertirá el diseño lógico en un archivo físico que se puede descargar en el dispositivo de destino (por ejemplo, Virtex FPGA).

### Esto involucra a tres sub-etapas:

- > Traducción de la netlist ( lista de red),

- Cartografía

- > Lugar de carreteras y planos.

### 2.8.5 Configuración de dispositivos

Esto se refiere a la programación real de la meta de FPGA mediante la descarga del archivo de programación de la FPGA de Xilinx.

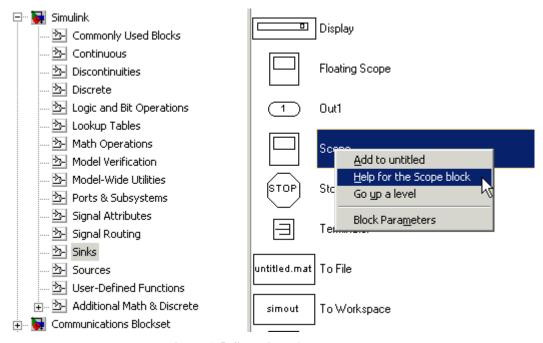

### 2.8.6 La ventana navegador de proyectos (Proyect Navigator)

Los pasos anteriores se gestionan a través de una ventana central ISE Project Navigator, que se muestra a continuación.

Fig 4. Ventana del ISE Project (clip de pantalla de Xilinx (TM) ISE).

### 2.8.7 La ventana de fuentes (Sources)

Esta ventana contiene los archivos de diseño de la fuente de un proyecto. Estos son los archivos de código fuente que haya creado o añadido al proyecto (véase más adelante). Una lista desplegable en la parte superior de las fuentes de la ventana le permite seleccionar los archivos de código fuente que están asociados con un aspecto particular diseño como la síntesis / o aplicación de simulación.

### 2.8.8 La ventana de procesos (Processes)

Las ventanas de los procesos de la lista de procesos disponibles (correspondientes a los procesos seleccionados en la ventana de procesos). Normalmente se selecciona un proceso particular que desea llevar a cabo en la fuente de archivo seleccionado. Esto puede incluir una simulación, ejecución, etc. Para ejecutar un proceso que puede hacer doble clic sobre el proceso. Cuando un proceso se ha ejecutado con éxito una marca roja-apagada\_ icono. Cuando se ejecuta un proceso de alto nivel, el Navegador de proyecto se ejecutará automáticamente a todos los asociados a procesos de nivel inferior.

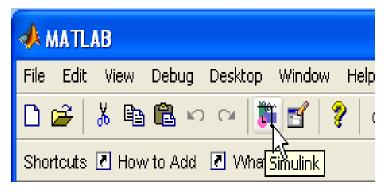

### 2.9.0 INTRODUCCIÓN A MATLAB Y SIMULINK.

Matlab es un programa de gran aceptación en ingeniería destinado realizar cálculos técnicos científicos y de propósito general. En el se integran operaciones

de cálculo, visualización y programación, donde la interacción con el usuario emplea una notación Matemática clásica.

### Los usos y aplicaciones típicos de Matlab son:

- Matemáticas y cálculo.

- Desarrollo de algoritmos.

- Adquisición de datos.

- Modelado, simulación y prototipado.

- Análisis y procesado de datos.

- Gráficos científicos y de ingeniería.

### 2.9.1 Desarrollo de aplicaciones utilizando Matlab en FPGAS.

El tipo básico de variable con el que trabaja Matlab es una matriz que no requiere ser dimensionada previamente en la declaración.

Una de las características más interesantes consiste en que el algebra vectorial y matricial se expresa con la misma sintaxis que las operaciones aritméticas escalares. Por ejemplo, en lenguaje C, para realizar la suma de dos variables enteras o reales b y c, escribiremos:

a = b+c; Mientras que en Matlab, emplearemos la misma sentencia tanto si b y c son enteros, reales, vectores o matrices.

### 2.9.2 Componentes de MATLAB

Matlab consta de cinco partes fundamentales:

- Entorno de desarrollo: Se trata de un conjunto de utilidades que permiten el Uso de funciones Matlab y ficheros en general. Muchas de estas utilidades son Interfaces graficas de usuario. Incluye el espacio de trabajo Matlab y la ventana de comandos.

- 2. La librería de funciones matemáticas Matlab. Se trata de un amplio conjunto de algoritmos de cálculo, comprendiendo las funciones más elementales como la suma, senos y cosenos o la aritmética compleja, hasta funciones más sosticadas como la inversión de matrices, el cálculo de autovalores, funciones de Bessel y transformadas rápidas de Fourier.

- 3. Gráficos. Matlab dispone de un conjunto de utilidades destinadas a visualizar vectores y matrices en forma de gráficos. Existe una gran cantidad de posibilidad ajustar el aspecto de los gráficos, destacando la visualización tridimensional con opciones de iluminación y sombreado, y la posibilidad de crear animaciones.

- **4. El interfaz de aplicación de Matlab** (**API**). Consiste en una librería que permite escribir programas ejecutables independientes en C y otros lenguajes, accediendo, mediante DLLs, a las utilidades de cálculo matricial de Matlab.

La gestión de complementos de Matlab se realiza mediante lo que se denominan toolboxes (paquetes de herramientas).

Un Toolbox de Matlab es un conjunto de funciones y algoritmos de cálculo especializados en un área de conocimiento: finanzas, tratamiento de señales, teoría de sistemas, etc.

#### 2.10. SIMULINK.

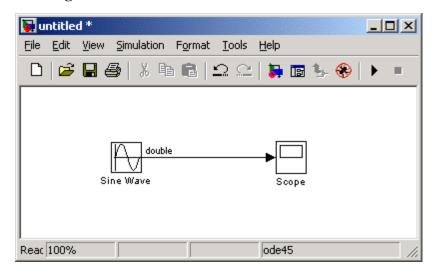

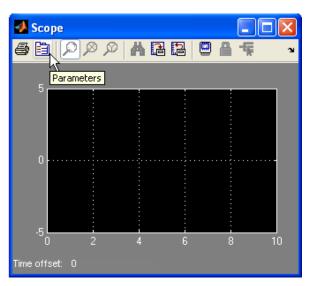

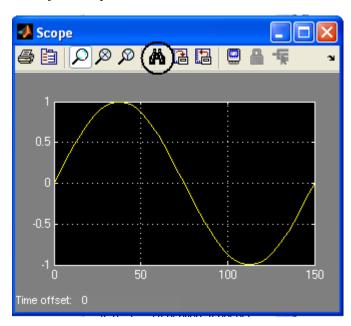

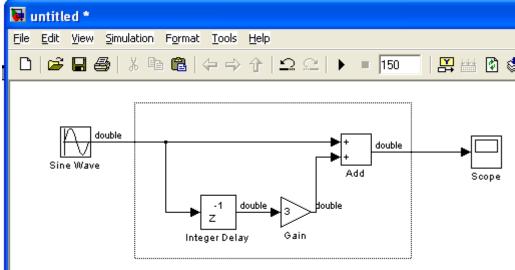

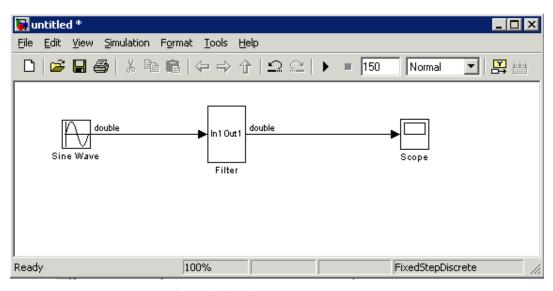

Simulink es una aplicación que permite construir y simular modelos de sistemas Físicos y sistemas de control mediante diagramas de bloques. El comportamiento de dichos sistemas se define mediante funciones de transferencia, operaciones matemáticas, elementos de Matlab y señales predefinidas de todo tipo.

Simulink dispone de una serie de utilidades que facilitan la visualización, análisis y guardado de los resultados de simulación. Simulink se emplea profusamente en ingeniería de control.

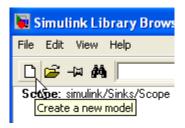

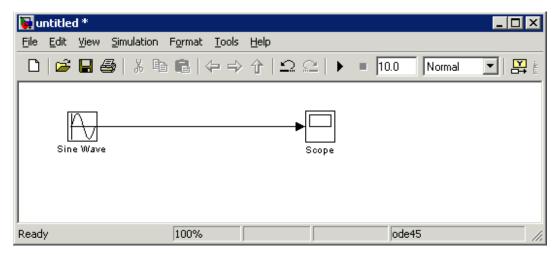

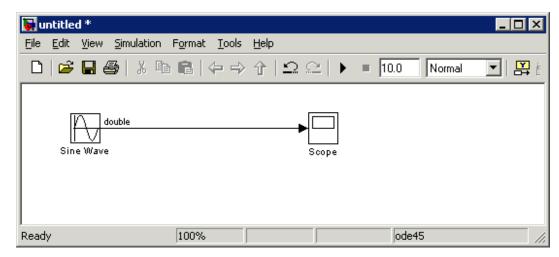

### 2.10.1 El entorno de trabajo de Simulink

Simulink es una herramienta de gran utilidad para la simulación de sistemas dinámicos. Principalmente, se trata de un entorno de trabajo grafico, en el que se especifican las partes de un sistema y su interconexión en forma de diagrama de bloques. De nuevo, se trata de una herramienta amplísima que además se complementa con numerosos elementos opcionales. Por tanto, nos limitaremos a dar unas pinceladas de los elementos más útiles en Regulación Automática.

Además de las capacidades de simulación de las que está dotado Simulink, conviene destacar que contiene cómodas utilidades de visualización y almacenamiento de resultados de simulación.

# **2.11.0** Sistema De Control De Caja De Herramientas (Control System Toolbox)

Diseño y análisis de sistemas de control

Fig.5 Gráfica de un sistema de control usando caja de herramientas

Control System Toolbox ofrece herramientas especializadas para analizar, diseñar y ajustar de forma sistemática sistemas de control lineales. Puede especificar un modelo lineal en su sistema, representar gráficamente sus respuestas de tiempo y frecuencia para comprender su comportamiento, ajustar los parámetros del controlador usando técnicas automatizadas e interactivas y verificar los requisitos de rendimiento tales como el tiempo de subida y los márgenes de ganancia y fase. Las interfaces gráficas de usuario (GUI) basadas en el flujo de trabajo le guían por cada paso del proceso de análisis y diseño.

### 2.11.1 Características Principales De La Caja De Herramientas

Facilita el diseño de sistemas de control de un solo bucle o de varios bucles usando una gran variedad de técnicas clásicas y de espacio de estado.

Permite analizar las respuestas y el rendimiento del sistema usando una interfaz gráfica de usuario (GUI) o las funciones de la línea de comando.

Ajusta manual o automáticamente los bucles SISO en los modelos de Simulink (con Simulink Control Design, disponible por separado).

Optimiza el rendimiento del sistema de control ajustándolo a los requisitos de tiempo y frecuencia (con Simulink Design Optimization, disponible por separado).

Representa y manipula modelos lineales como objetos de datos de función de transferencia, espacio de estado, ganancia de polo cero y respuesta de frecuencia. Convierte entre representaciones de modelos, discretiza modelos de tiempo continuo y calcula las aproximaciones de orden bajo de los sistemas de orden alto. Utiliza algoritmos innovadores integrados en las bibliotecas LAPCAK y SLICOT para lograr una precisión y un rendimiento óptimos.

### 2.11.2 Usos de la Caja De Herramientas

Las técnicas de control lineal constituyen la base del diseño y análisis de sistemas de control. Control System Toolbox le permite crear modelos lineales de sus sistemas de control. Usando herramientas de visualización interactiva, puede analizar estos modelos para comprender su comportamiento, rendimiento y

limitaciones. También puede ajustar de forma sistemática los parámetros del sistema de control usando técnicas de diseño de un solo bucle o de varios bucles. Los modelos lineales de Control System Toolbox se pueden utilizar en otros productos de diseño de sistemas de control, tales como Robust Control Toolbox y Model Predictive Control Toolbox. Junto con Simulink Control Design y Simulink Design Optimization, Control System Toolbox proporciona un conjunto de herramientas completo que, utilizando una interfaz gráfica de usuario, permite analizar y ajustar los sistemas de control generados en Simulink.

### 2.12.0 APLICACIONES DE LA FPGA

Cualquier circuito de aplicación específica puede ser implementado en un FPGA, siempre y cuando esta disponga de los recursos necesarios. Las aplicaciones donde más comúnmente se utilizan los FPGA incluyen a los DSP (procesamiento digital de señales), radio definido por software, sistemas aeroespaciales y de defensa, prototipos de ASICs, sistemas de imágenes para medicina, sistemas de visión para computadoras, reconocimiento de voz, bioinformática, emulación de hardware de computadora, entre otras. Cabe notar que su uso en otras áreas es cada vez mayor, sobre todo en aquellas aplicaciones que requieren un alto grado de paralelismo.

Existe código fuente disponible (bajo licencia GNU GPL)<sup>1</sup> de sistemas como microprocesadores, microcontroladores, filtros, módulos de comunicaciones y memorias, entre otros. Estos códigos se llaman **cores**.

# **CAPITULO III**

## Filtro digital FIR (Finite Impulse Response)

## (Respuesta al Impulso Finita))

### 3.1.0 QUE ES UN FILTRO DIGITAL FIR?

FIR es un acrónimo en inglés para Finite Impulse Response o Respuesta finita al impulso.

Es un tipo de filtro digital que si su entrada es un impulso (una delta de Kronecker) la salida será un número limitado de términos no nulos.

Para obtener la salida sólo se emplean valores de entrada actuales y anteriores.

También se llaman filtros digitales no-recursivos. Su expresión en el dominio discreto es:  $g_n = \sum_{k=0}^{N-1} b_k x (n-k)$

El orden del filtro está dado por N, es decir, el número de coeficientes.

También la salida puede ser expresada como la convolución de una señal de entrada x[n] con un filtro h[n]:  $y_n = \sum_{k=0}^{N-1} h_k x_{n-k}$

### 3.2.0 ESTRUCTURA DEL FILTRO FIR

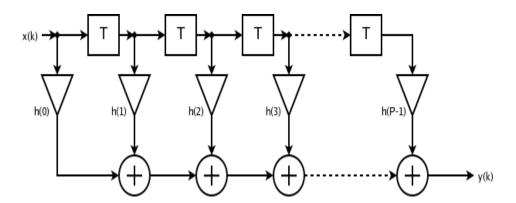

La estructura de un filtro FIR por tanto es la siguiente:

Fig. 1 Grafica de la estructura del Filtro Fir

La cual puede verse reflejada en la aplicación de la transformada Z:

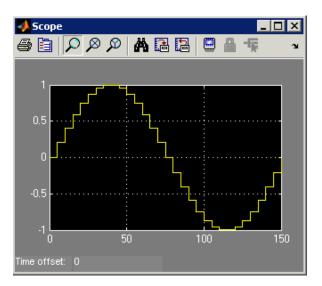

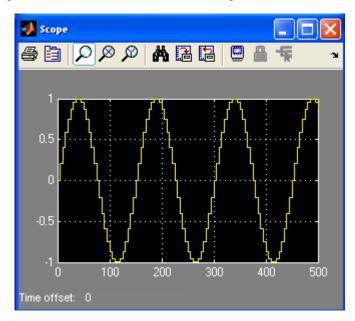

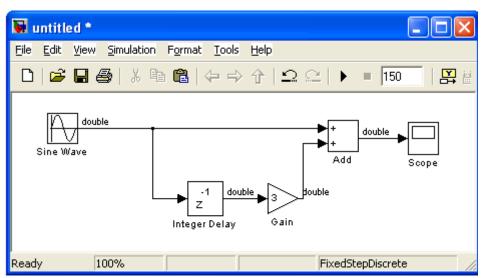

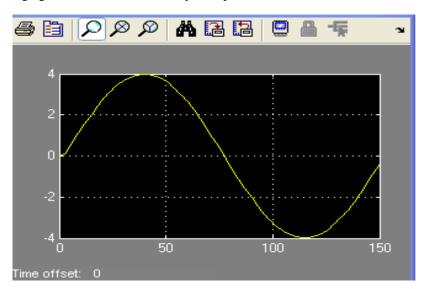

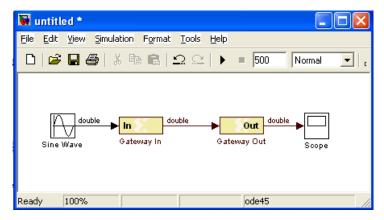

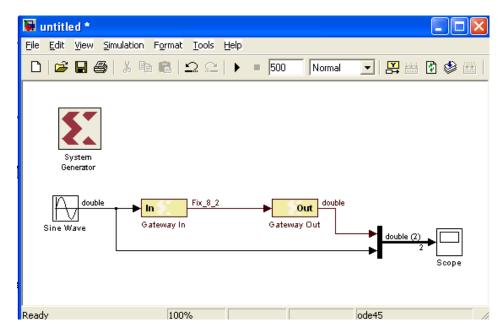

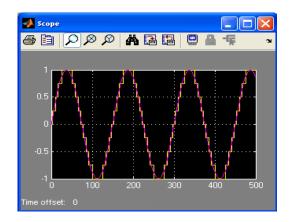

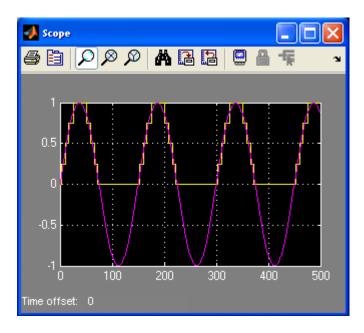

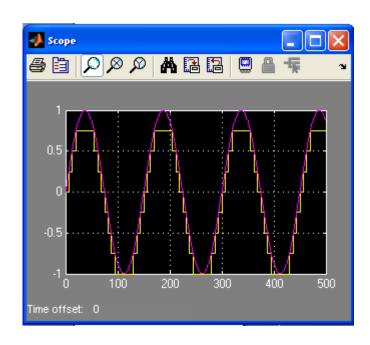

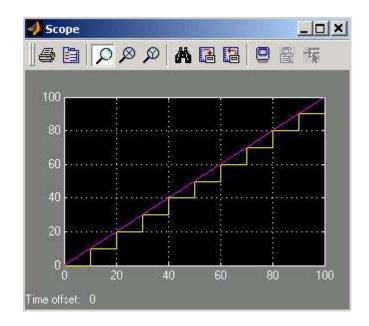

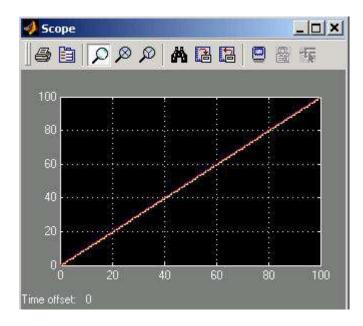

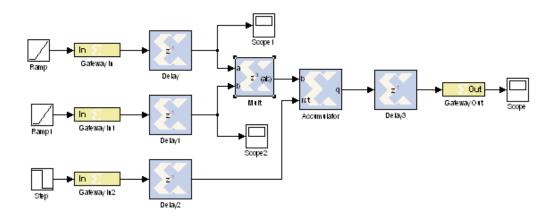

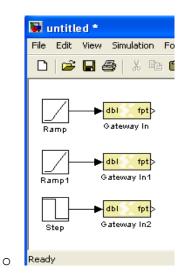

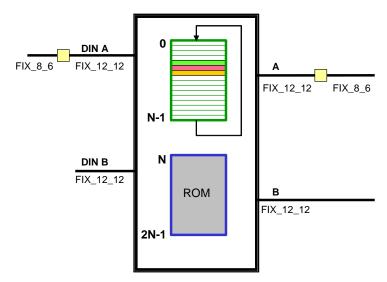

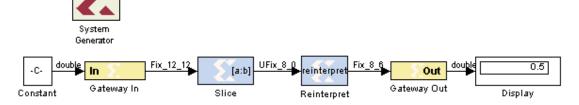

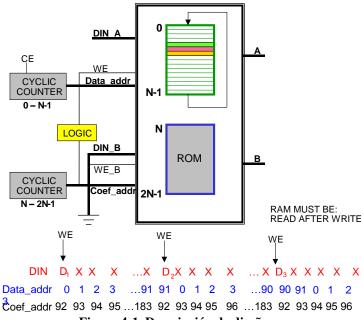

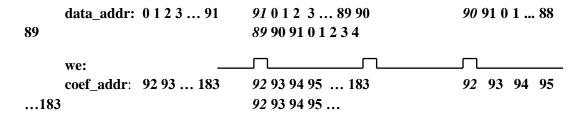

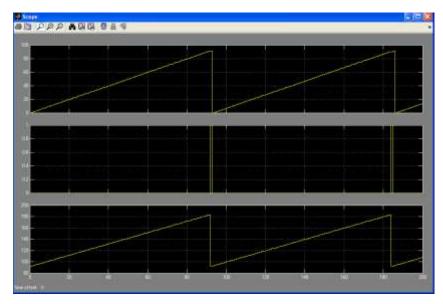

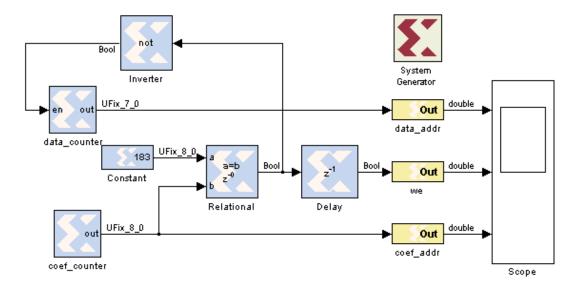

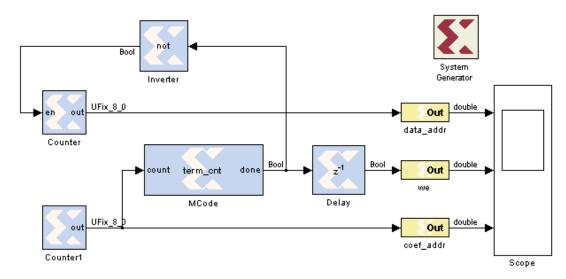

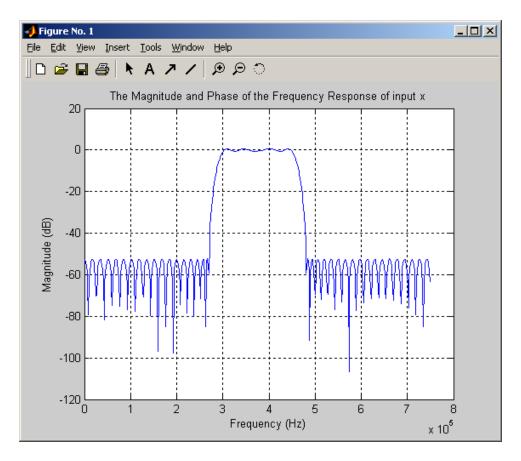

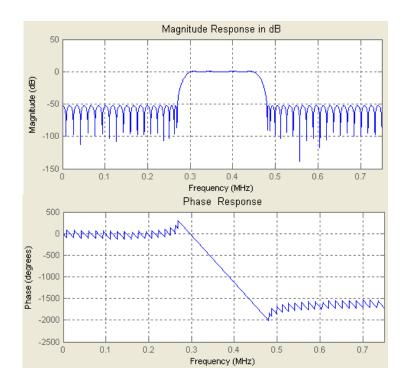

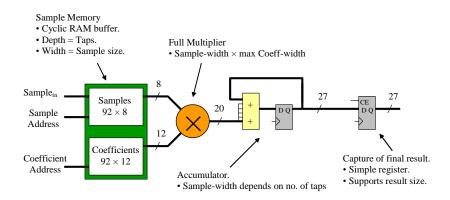

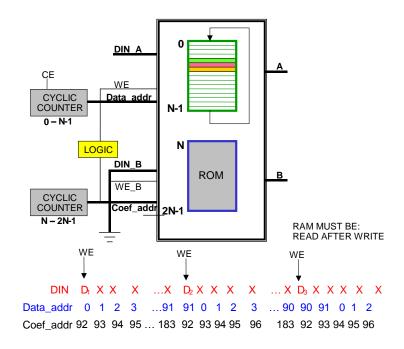

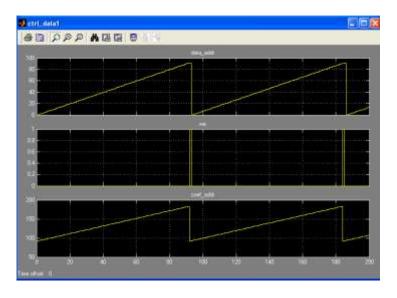

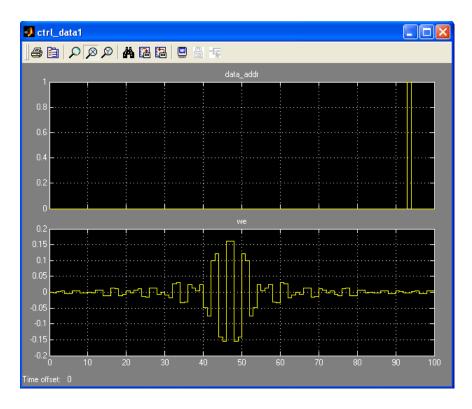

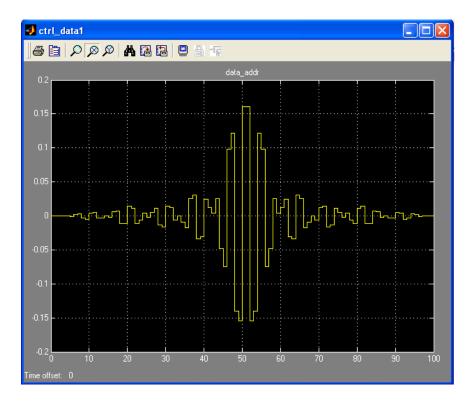

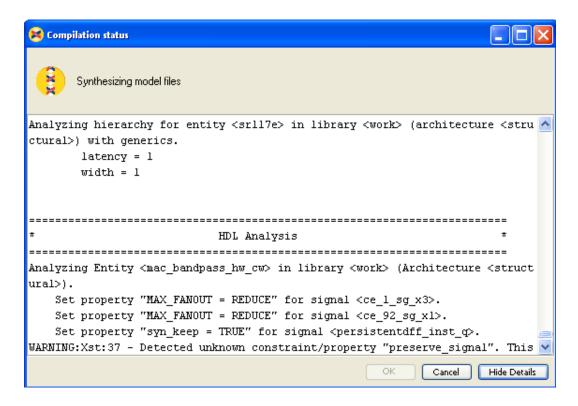

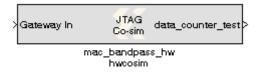

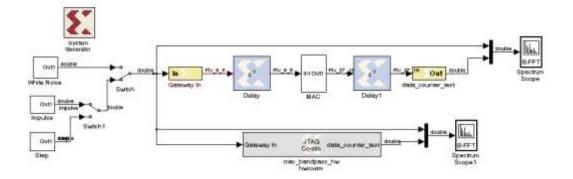

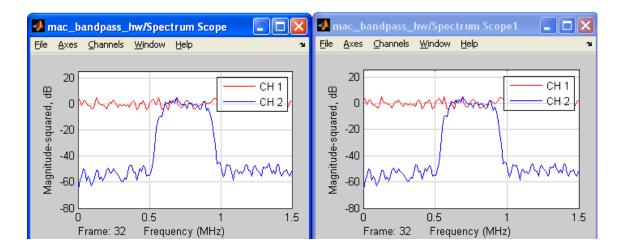

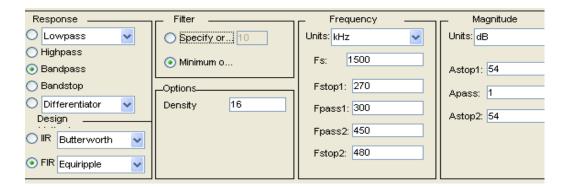

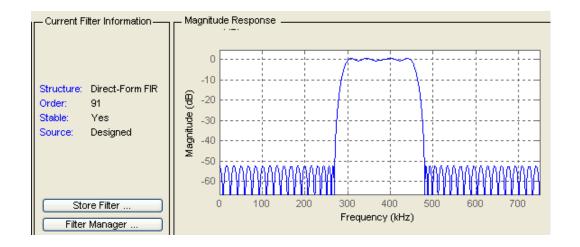

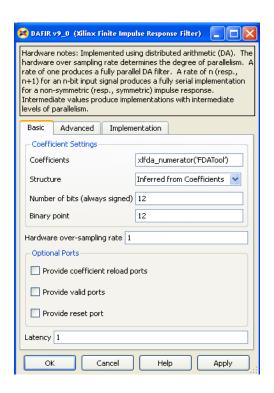

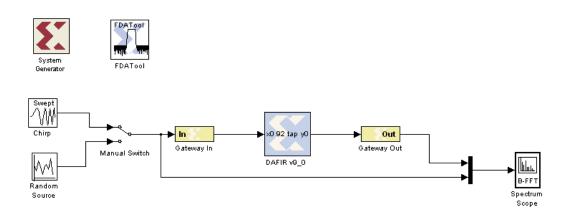

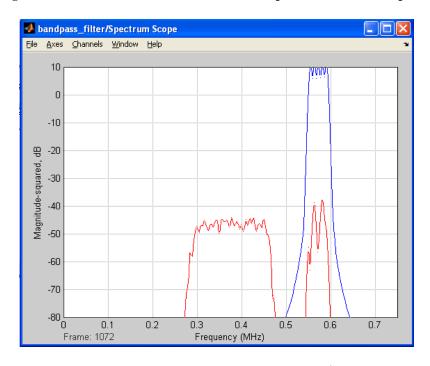

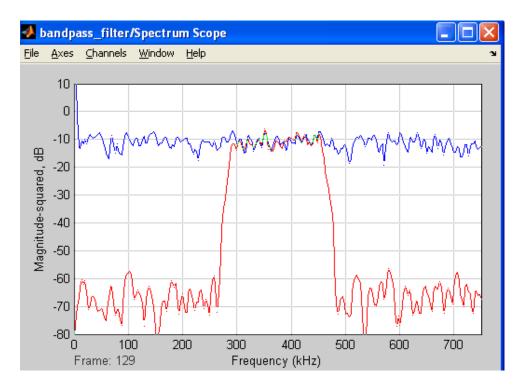

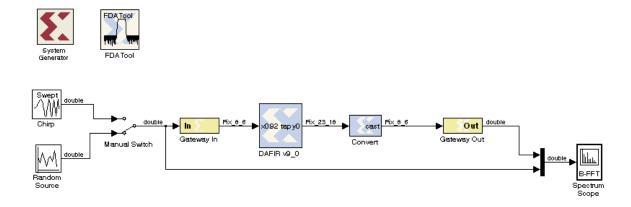

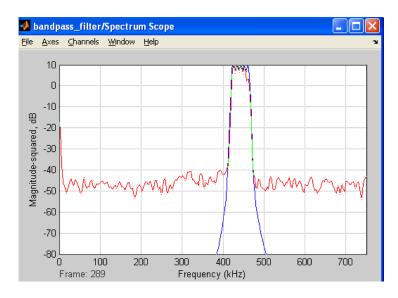

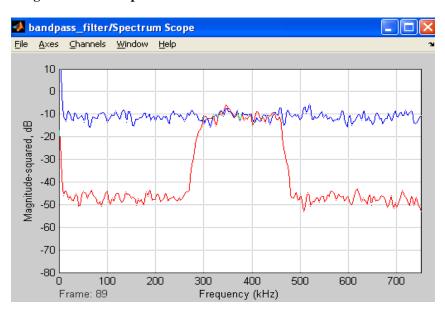

$$H(z) = \sum_{k=0}^{N-1} h_k z^{-k} = h_0 + h_1 z^{-1} + \dots + h_{N-1} z^{-(N-1)}$$